Figure 20. olm configuration #4, 1 spi mode, Figure 21. control port timing in spi mode – Cirrus Logic CS42428 User Manual

Page 35

DS605F2

35

CS42428

4.6.1

SPI Mode

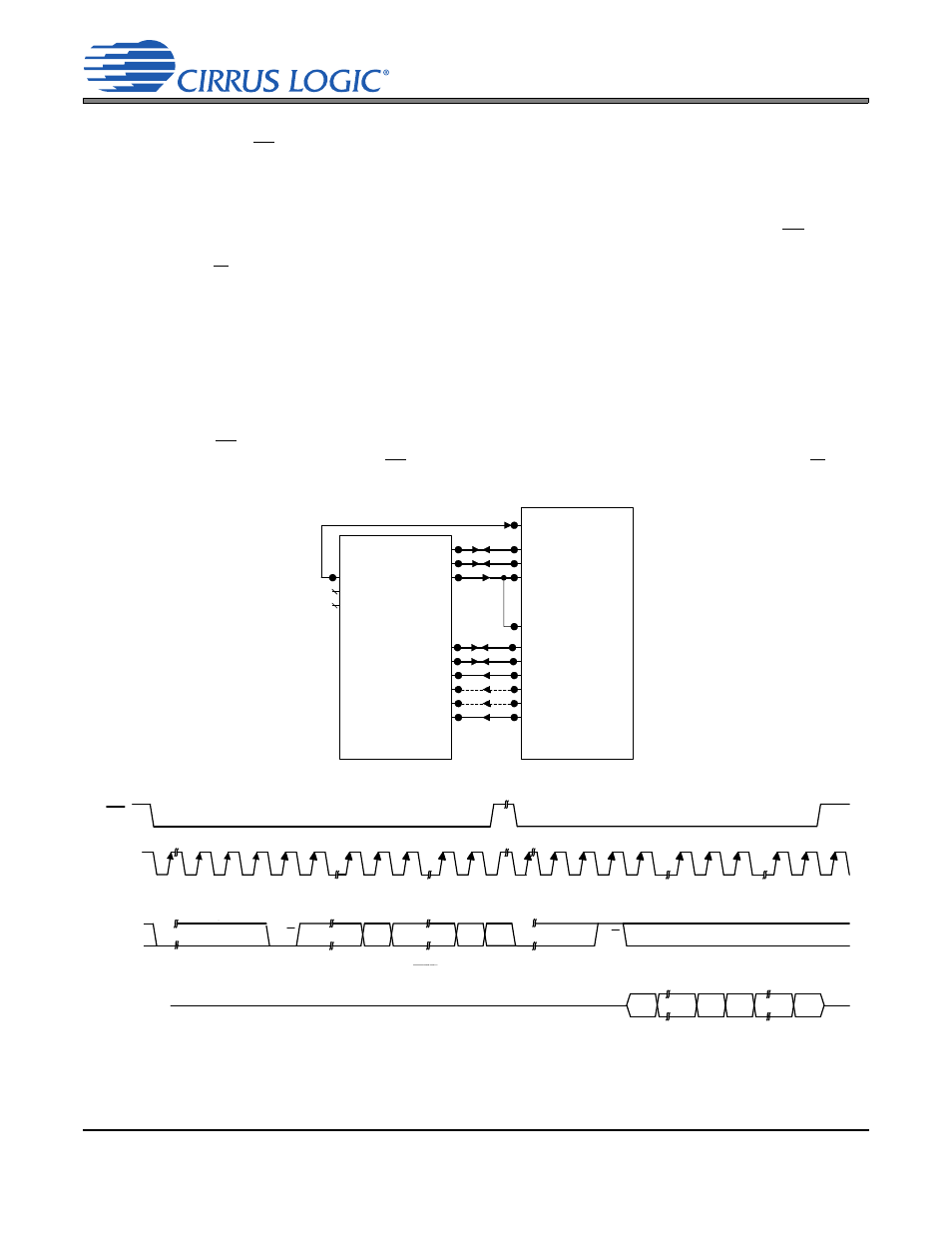

In SPI mode, CS is the CS42428 chip-select signal; CCLK is the control port bit clock (input into the

CS42428 from the microcontroller); CDIN is the input data line from the microcontroller, and CDOUT is

the output data line to the microcontroller. Data is clocked in on the rising edge of CCLK and out on the

falling edge.

shows the operation of the control port in SPI mode. To write to a register, bring CS low. The

first seven bits on CDIN form the chip address and must be 1001111. The eighth bit is a read/write indi-

cator (R/W), which should be low to write. The next eight bits form the Memory Address Pointer (MAP),

which is set to the address of the register that is to be updated. The next eight bits are the data which will

be placed into the register designated by the MAP. During writes, the CDOUT output stays in the Hi-Z

state. It may be externally pulled high or low with a 47 k

resistor, if desired.

There is a MAP auto-increment capability, enabled by the INCR bit in the MAP register. If INCR is a zero,

the MAP will stay constant for successive read or writes. If INCR is set to a 1, the MAP will auto-increment

after each byte is read or written, allowing block reads or writes of successive registers.

To read a register, the MAP has to be set to the correct address by executing a partial write cycle which

finishes (CS high) immediately after the MAP byte. The MAP auto increment bit (INCR) may be set or not,

as desired. To begin a read, bring CS low, send out the chip address and set the read/write bit (R/W) high.

The next falling edge of CCLK will clock out the MSB of the addressed register (CDOUT will leave the high

SCLK_PORT1

LRCK_PORT1

SDIN_PORT1

SDIN_PORT2

SCLK_PORT2

LRCK_PORT2

SDOUT1_PORT2

SDOUT2_PORT2

SDOUT3_PORT2

SDOUT4_PORT2

RMCK

ADCIN1

ADCIN2

64Fs,128Fs, 256Fs

DIGITAL AUDIO

PROCESSOR

ADC_SCLK

ADC_LRCK

ADC_SDOUT

DAC_SCLK

DAC_LRCK

DAC_SDIN1

DAC_SDIN2

DAC_SDIN3

DAC_SDIN4

64Fs,128Fs

MCLK

Figure 20. OLM Configuration #4

CS42426

M A P

MSB

LSB

DATA

b y te 1

b y te n

R/W

R/W

A D D R E S S

C H IP

ADDRESS

C H IP

C D IN

C C L K

CS

C D O U T

MSB

LSB MSB

LSB

1001111

1001111

MAP = Memory Address Pointer, 8 bits, MSB first

High Impedance

Figure 21. Control Port Timing in SPI Mode