Cirrus Logic CS42428 User Manual

Features, General description, Eight 24-bit d/a, two 24-bit a/d converters

Copyright

Cirrus Logic, Inc. 2014

(All Rights Reserved)

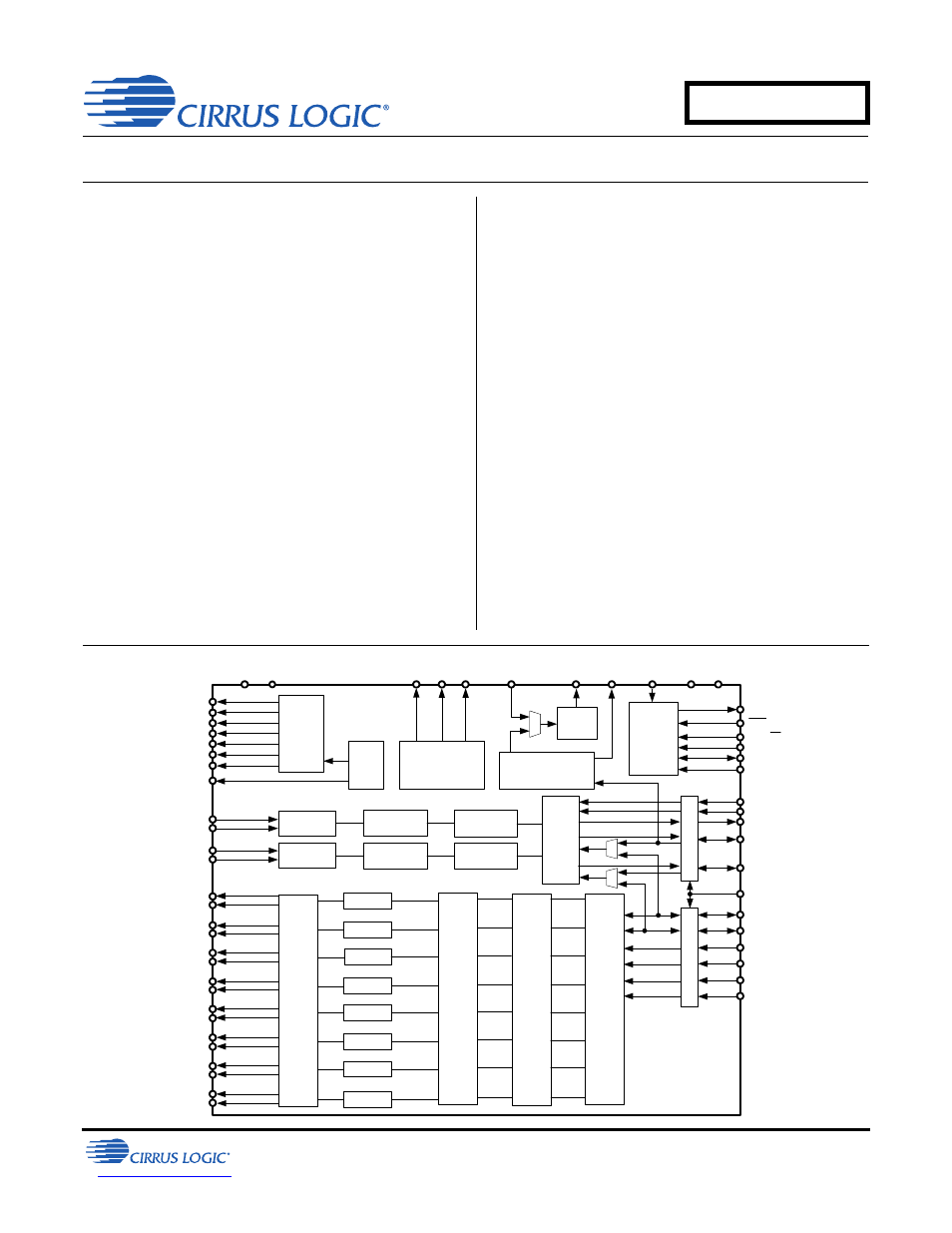

114 dB, 192-kHz 8-Ch CODEC with PLL

Features

Eight 24-bit D/A, two 24-bit A/D Converters

114 dB DAC / 114 dB ADC Dynamic Range

-100 dB THD+N

System Sampling Rates up to 192 kHz

Integrated Low-Jitter PLL for Increased System

Jitter Tolerance

PLL Clock or System Clock Selection

7 Configurable General-Purpose Outputs

ADC High-Pass Filter for DC Offset Calibration

Expandable ADC Channels and One-Line

Mode Support

Digital Output Volume Control with Soft Ramp

Digital ±15 dB Input Gain Adjust for ADC

Differential Analog Architecture

Supports Logic Levels between 1.8 V and 5 V

General Description

The CS42428 provides two analog-to-digital and eight

digital-to-analog delta-sigma converters, as well as an

integrated PLL.

The CS42428 integrated PLL provides a low-jitter sys-

tem clock. The internal stereo ADC is capable of

independent channel gain control for single-ended or

differential analog inputs. All eight channels of DAC pro-

vide digital volume control and differential analog

outputs. The general-purpose outputs may be driven

high or low, or mapped to a variety of DAC mute con-

trols or ADC overflow indicators.

The CS42428 is ideal for audio systems requiring wide

dynamic range, negligible distortion and low noise, such

as A/V receivers, DVD receivers, and digital speakers.

The CS42428 is available in a 64-pin LQFP package in

Commercial (-10° to +70° C) grades. The CDB42428

Customer Demonstration board is also available for de-

vice evaluation. Refer to

PLL

Internal Voltage

Reference

RST

GPO1

AD0/CS

SCL/CCLK

SDA/CDOUT

AD1/CDIN

VLC

AOUTA1+

AOUTA1-

AOUTB1+

AOUTA3+

AOUTA3-

AOUTA2-

AOUTB2-

AOUTA2+

AOUTB2+

AOUTB1-

AOUTB3+

AOUTB3-

AOUTA4+

AOUTA4-

AOUTB4+

AOUTB4-

AINL+

AINL-

AINR+

AINR-

FILT+

REFGND VQ

ADC#1

ADC#2

Digital Filter

Digital Filter

Gain & Clip

Gain & Clip

DAC_SCLK

DAC_LRCK

DAC_SDIN4

DAC_SDIN3

DAC_SDIN2

DAC_SDIN1

VLS

DGND VD

OMCK

RMCK LPFLT

INT

Control

Port

DAC#1

DAC#2

DAC#3

DAC#4

DAC#5

DAC#6

DAC#7

DAC#8

D

igi

ta

l F

ilte

r

Vo

lu

m

e C

o

nt

ro

l

GPO2

GPO3

GPO4

GPO5

GPO6

GPO7

MUTEC

Mute

A

n

al

og

F

ilt

er

VA AGND

Mult/Div

GPO

Le

vel T

ra

n

sla

to

r

DAC S

eri

a

l A

u

di

o

P

o

rt

ADC_SDOUT

ADCIN1

ADCIN2

ADC_LRCK

ADC

Serial

Audio

Port

ADC_SCLK

Le

ve

l T

ra

ns

la

to

r

MAR '14

DS605F2

CS42428

Document Outline

- 1. Characteristics and Specifications

- Specified Operating Conditions

- Absolute Maximum Ratings

- Analog Input Characteristics

- A/D Digital Filter Characteristics

- Analog Output Characteristics

- D/A Digital Filter Characteristics

- Switching Characteristics

- Switching Characteristics - Control Port - I²C™ Format

- Switching Characteristics - Control Port - SPI™ Format

- DC Electrical Characteristics

- Digital Interface Characteristics

- 2. Pin Descriptions

- 3. Typical Connection Diagrams

- 4. Applications

- 4.1 Overview

- 4.2 Analog Inputs

- 4.3 Analog Outputs

- 4.4 Clock Generation

- 4.5 Digital Interfaces

- 4.6 Control Port Description and Timing

- 4.7 Interrupts

- 4.8 Reset and Power-Up

- 4.9 Power Supply, Grounding, and PCB Layout

- 5. Register Quick Reference

- 6. Register Description

- Table 5. DAC De-Emphasis

- Table 6. Digital Interface Formats

- Table 7. ADC One-Line Mode

- Table 8. DAC One-Line Mode

- Table 9. RMCK Divider Settings

- Table 10. OMCK Frequency Settings

- Table 11. Master Clock Source Select

- Table 12. PLL Clock Frequency Detection

- Table 13. Example Digital Volume Settings

- Table 14. ATAPI Decode

- Table 15. Example ADC Input Gain Settings

- 7. Parameter Definitions

- 8. Appendix A: External Filters

- 9. Appendix B: PLL Filter

- 10. Appendix C: ADC Filter Plots

- Figure 27. Single-Speed Mode Stopband Rejection

- Figure 28. Single-Speed Mode Transition Band

- Figure 29. Single-Speed Mode Transition Band (Detail)

- Figure 30. Single-Speed Mode Passband Ripple

- Figure 31. Double-Speed Mode Stopband Rejection

- Figure 32. Double-Speed Mode Transition Band

- Figure 33. Double-Speed Mode Transition Band (Detail)

- Figure 34. Double-Speed Mode Passband Ripple

- Figure 35. Quad-Speed Mode Stopband Rejection

- Figure 36. Quad-Speed Mode Transition Band

- Figure 37. Quad-Speed Mode Transition Band (Detail)

- Figure 38. Quad-Speed Mode Passband Ripple

- 11. Appendix D: DAC Filter Plots

- Figure 39. Single-Speed (fast) Stopband Rejection

- Figure 40. Single-Speed (fast) Transition Band

- Figure 41. Single-Speed (fast) Transition Band (detail)

- Figure 42. Single-Speed (fast) Passband Ripple

- Figure 43. Single-Speed (slow) Stopband Rejection

- Figure 44. Single-Speed (slow) Transition Band

- Figure 45. Single-Speed (slow) Transition Band (detail)

- Figure 46. Single-Speed (slow) Passband Ripple

- Figure 47. Double-Speed (fast) Stopband Rejection

- Figure 48. Double-Speed (fast) Transition Band

- Figure 49. Double-Speed (fast) Transition Band (detail)

- Figure 50. Double-Speed (fast) Passband Ripple

- Figure 51. Double-Speed (slow) Stopband Rejection

- Figure 52. Double-Speed (slow) Transition Band

- Figure 53. Double-Speed (slow) Transition Band (detail)

- Figure 54. Double-Speed (slow) Passband Ripple

- Figure 55. Quad-Speed (fast) Stopband Rejection

- Figure 56. Quad-Speed (fast) Transition Band

- Figure 57. Quad-Speed (fast) Transition Band (detail)

- Figure 58. Quad-Speed (fast) Passband Ripple

- Figure 59. Quad-Speed (slow) Stopband Rejection

- Figure 60. Quad-Speed (slow) Transition Band

- Figure 61. Quad-Speed (slow) Transition Band (detail)

- Figure 62. Quad-Speed (slow) Passband Ripple

- 12. Package Dimensions

- 13. Ordering Information

- 14. References

- 15. Revision History