Single – Cirrus Logic CS42426 User Manual

Page 43

DS604F2

43

CS42426

6.3

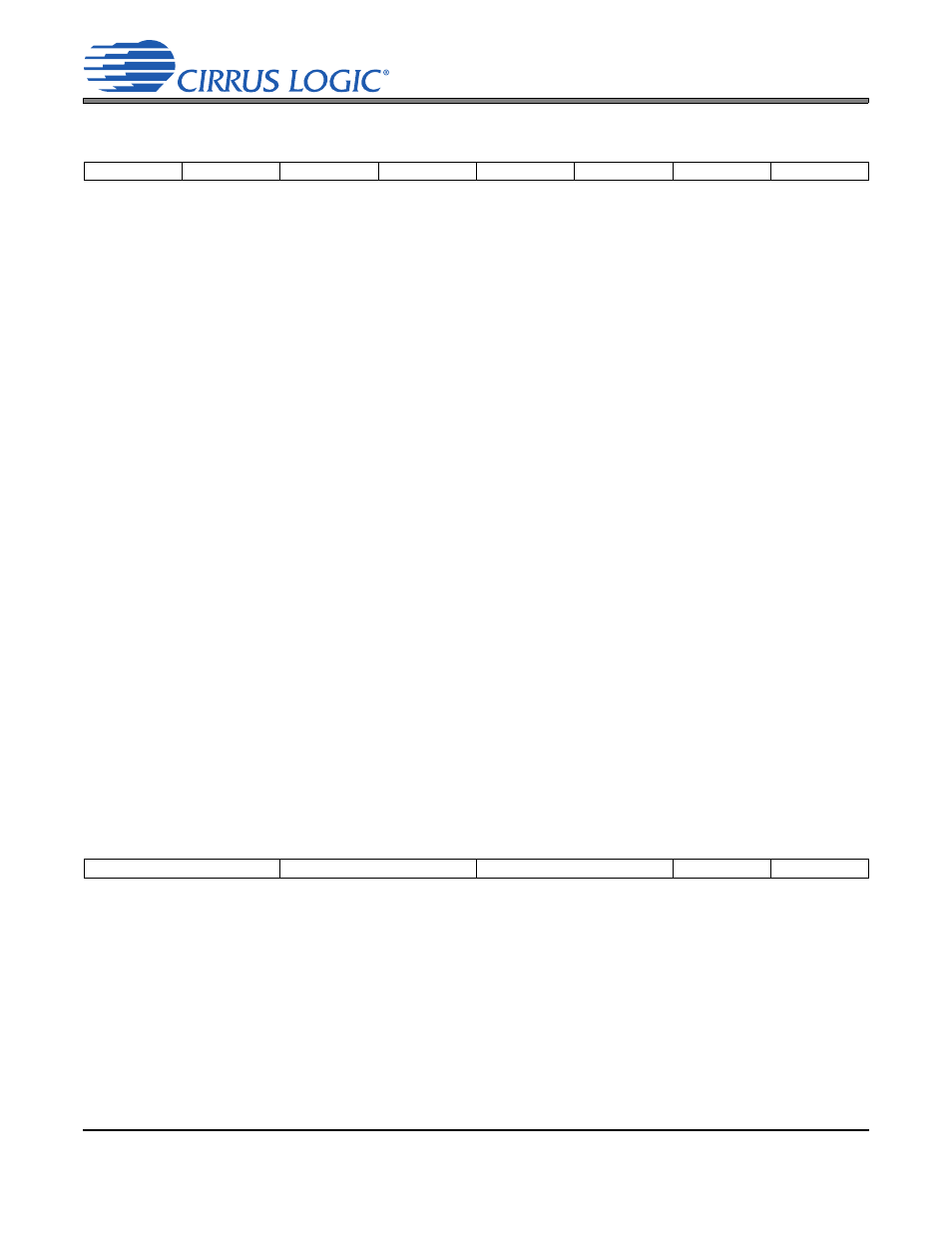

Power Control (address 02h)

6.3.1

POWER DOWN PLL (PDN_PLL)

Default = 0

Function:

When enabled, the PLL is held in a reset state. It is advised that any change of this bit be made while

the DACs are muted or the power-down bit (PDN) is enabled to eliminate the possibility of audible

artifacts.

6.3.2

POWER DOWN ADC (PDN_ADC)

Default = 0

Function:

When enabled the stereo analog to digital converter will remain in a reset state. It is advised that any

change of this bit be made while the DACs are muted or the power-down bit (PDN) is enabled to elim-

inate the possibility of audible artifacts.

6.3.3

POWER DOWN DAC PAIRS (PDN_DACX)

Default = 0

Function:

When enabled the respective DAC channel pair x (AOUTAx and AOUTBx) will remain in a reset state.

6.3.4

POWER DOWN (PDN)

Default = 1

Function:

The entire device will enter a low-power state when this function is enabled, and the contents of the

control registers are retained in this mode. The power-down bit defaults to ‘enabled’ on power-up and

must be disabled before normal operation can occur.

6.4

Functional Mode (address 03h)

6.4.1

DAC FUNCTIONAL MODE (DAC_FMX)

Default = 00

00 - Single-Speed Mode (4 to 50 kHz sample rates)

01 - Double-Speed Mode (50 to 100 kHz sample rates)

10 - Quad-Speed Mode (100 to 192 kHz sample rates)

11 - Reserved

Function:

Selects the required range of sample rates for all converters clocked from the DAC serial port (DAC_SP).

Bits must be set to the corresponding sample rate range when the DAC_SP is in Master or Slave Mode.

7

6

5

4

3

2

1

0

Reserved

PDN_PLL

PDN_ADC

Reserved

PDN_DAC3

PDN_DAC2

PDN_DAC1

PDN

7

6

5

4

3

2

1

0

DAC_FM1

DAC_FM0

ADC_FM1

ADC_FM0

Reserved

ADC_SP SEL

DAC_DEM

Reserved