4 clock generation, Figure 10. clock generation, 1 pll and jitter attenuation – Cirrus Logic CS42426 User Manual

Page 23

DS604F2

23

CS42426

4.4

Clock Generation

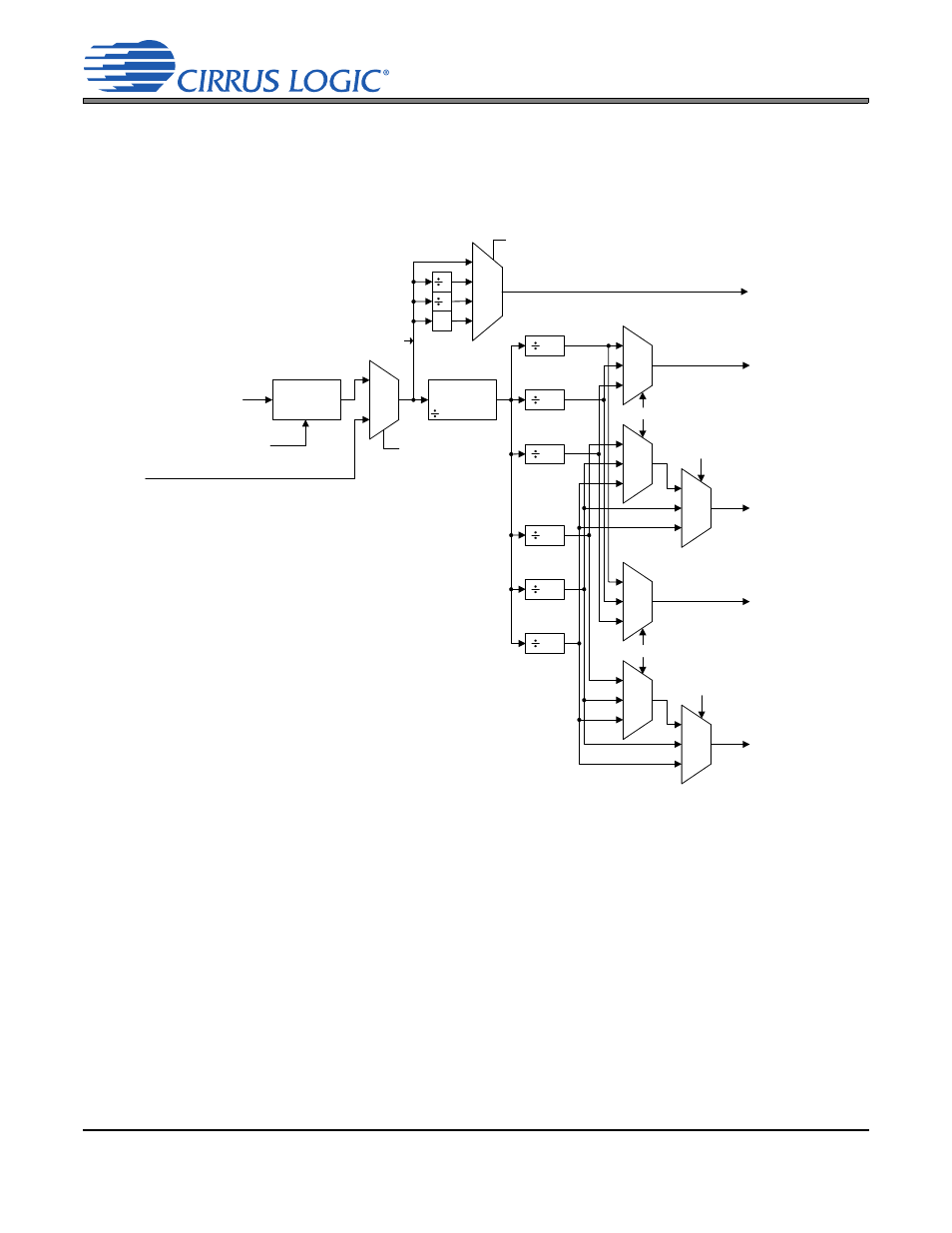

The clock generation for the CS42426

is shown in the figure below. The internal MCLK is derived from the

output of the PLL or a master clock source attached to OMCK. The mux selection is controlled by the SW_C-

TRLx bits and can be configured to manual switch mode only, or automatically switch on loss of PLL lock

to the other source input.

4.4.1

PLL and Jitter Attenuation

The PLL can be configured to lock onto the incoming ADC_LRCK signal from the ADC Serial Port and

generate the required internal master clock frequency. There are some applications where low jitter in the

recovered clock, presented on the RMCK pin, is important. For this reason, the PLL has been designed

to have good jitter-attenuation characteristics. By setting the PLL_LRCK bit to a ‘1’ in the register

Control (address 06h)” on page 48

, the PLL will lock to the incoming ADC_LRCK and generate an output

master clock (RMCK) of 256Fs.

Table 2

shows the output of the PLL with typical input Fs values for AD-

C_LRCK.

See

“Appendix B: PLL Filter” on page 62

for more information concerning PLL operation, required filter

components, optimal layout guidelines, and jitter-attenuation characteristics.

ADC_LRCK

(slave mode)

PLL (256Fs)

8.192 -

49.152 MHz

00

01

PLL_LRCK bit

SW_CTRLx bits

(manual or auto

switch)

OMCK

Auto Detect

Input Clock

1,1.5, 2, 4

single

speed

256

double

speed

128

quad

speed

64

single

speed

4

double

speed

2

quad

speed

1

00

01

10

00

01

10

00

01

10

00

01

10

not OLM

OLM #1

DAC_FMx bits

ADC_FMx bits

DAC_OLx

or ADC_OLx bits

ADC_OLx and

ADC_SP SELx bits

ADC_SCLK

DAC_SCLK

DAC_LRCK

ADC_LRCK

RMCK

OLM #2

not OLM

OLM #1

OLM #2

128FS

256FS

128FS

256FS

Internal

MCLK

00

01

10

11

RMCK_DIVx bits

2

4

X2

Figure 10. Clock Generation