4 olm config #4 – Cirrus Logic CS42426 User Manual

Page 34

34

DS604F2

CS42426

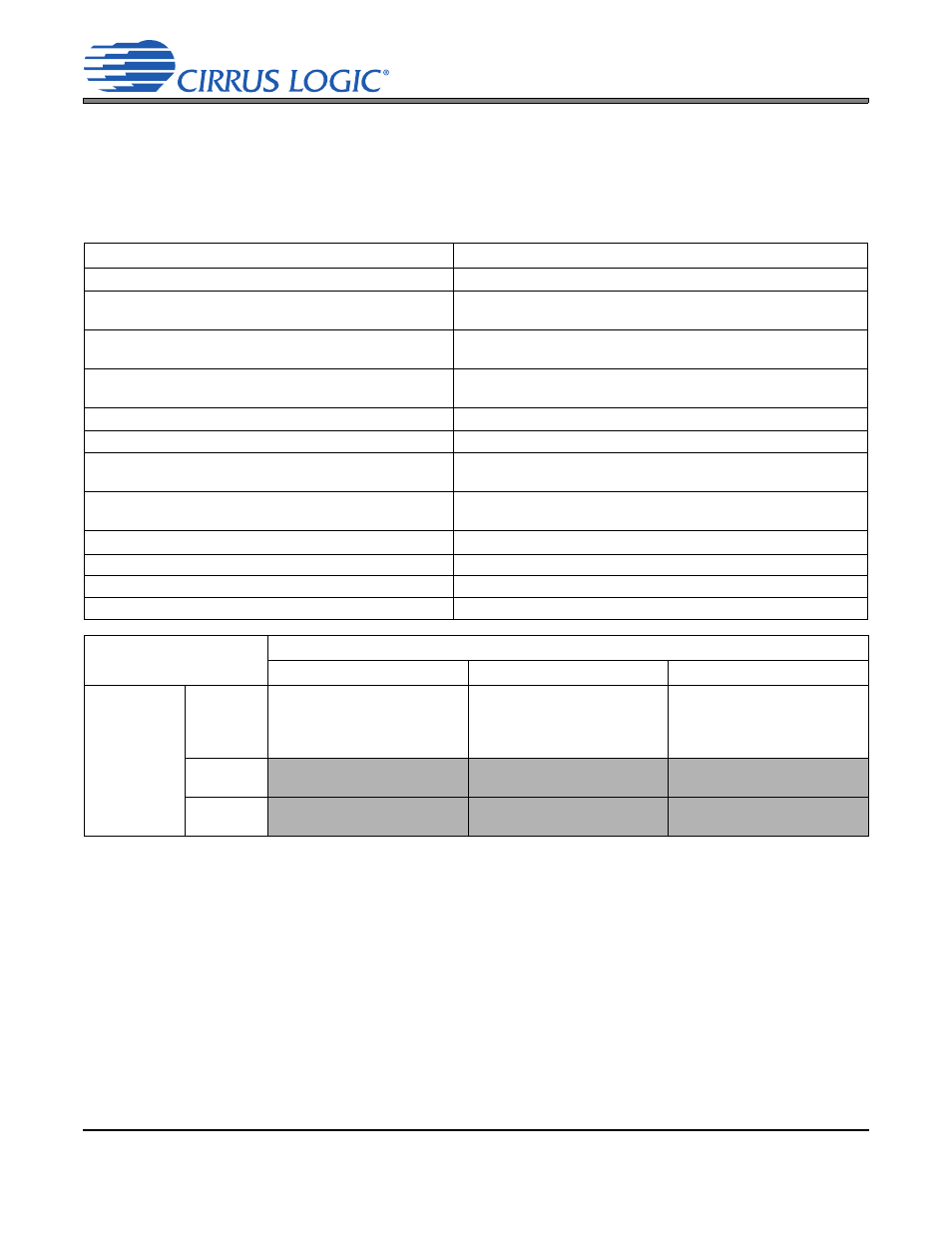

4.5.4.4 OLM Config #4

This One-Line Mode configuration can support up to 6 channels of DAC data on 2 DAC_SDIN pins and 2

channels of ADC data and will handle up to 24-bit samples at a sampling frequency of 48 kHz on all chan-

nels for both the DAC and ADC. The output data stream of the internal ADCs can be configured to run at

the DAC_SP clock speeds or to run at the ADC_SP rate. The DAC_SP and ADC_SP can operate at differ-

ent Fs rates.

Register / Bit Settings

Description

Functional Mode Register (addr = 03h)

Set DAC_FMx = 00,01,10

DAC_LRCK can run at SSM, DSM, or QSM independent of

ADC_LRCK

Set ADC_FMx = 00,01,10

ADC_LRCK can run at SSM, DSM, or QSM independent of

DAC_LRCK

Set ADC_CLK_SEL = 0 or 1

Configure ADC_SDOUT to be clocked from the ADC_SP or

DAC_SP clocks.

Interface Format Register (addr = 04h)

Set DIFx bits to proper serial format

Select the digital interface format when not in One-Line Mode

Set ADC_OLx bits = 00

Set ADC operating mode to Not One-Line Mode since only 2

channels of ADC are supported

Set DAC_OLx bits = 00,01,10

Select DAC operating mode, see table below for valid combina-

tions

Misc. Control Register (addr = 05h)

Set DAC_SP M/S = 0 or 1

Set DAC Serial Port to Master Mode or Slave Mode.

Set ADC_SP M/S = 0 or 1

Set ADC Serial Port to Master Mode or Slave Mode.

Set EXT ADC SCLK = 0

External ADCs are not used. Leave bit in default state.

DAC Mode

Not One-Line Mode

One-Line Mode #1

One-Line Mode #2

ADC Mode

Not One-

Line Mode

DAC_SCLK=64Fs/128Fs

DAC_LRCK=SSM/DSM/QSM

ADC_SCLK=64Fs/128Fs

ADC_LRCK=SSM/DSM/QSM

DAC_SCLK=128Fs

DAC_LRCK=SSM/DSM

ADC_SCLK=64Fs/128Fs

ADC_LRCK=SSM/DSM/QSM

DAC_SCLK=256Fs

DAC_LRCK=SSM

ADC_SCLK=64Fs/128Fs

ADC_LRCK=SSM/DSM/QSM

One-Line

Mode #1

not valid

not valid

not valid

One-Line

Mode #2

not valid

not valid

not valid