Switching characteristics, Figure 1. serial audio port master mode timing, Figure 2. serial audio port slave mode timing – Cirrus Logic CS42426 User Manual

Page 11

DS604F2

11

CS42426

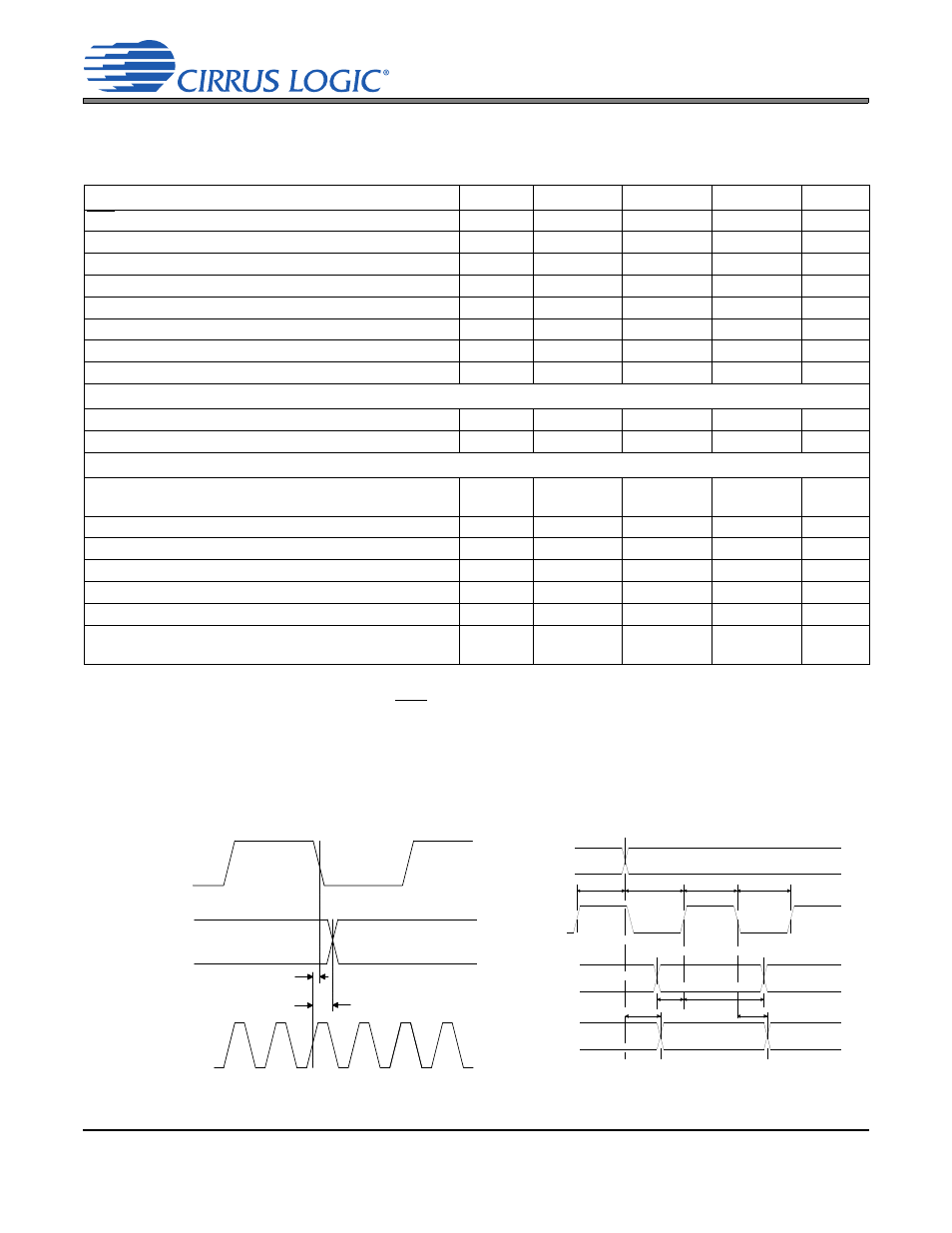

SWITCHING CHARACTERISTICS

(T

A

= -10 to +70° C; VA = 5 V, VD =VLC= 3.3 V, VLS = 1.8 V to 5.25 V; Inputs: Logic 0 = DGND, Logic 1 = VLS,

C

L

= 30 pF)

Notes:

12. After powering-up the CS42426, RST should be held low after the power supplies and clocks are set-

tled.

for suggested OMCK frequencies

14. Limit the loading on RMCK to 1 CMOS load if operating above 24.576 MHz.

15. Not valid when RMCK_DIV in

“Clock Control (address 06h)” on page 48

16. 76.5 ns for Single-Speed and Double-Speed modes, 23 ns for Quad-Speed Mode.

Parameters

Symbol

Min Typ

Max

Units

RST Pin Low Pulse Width

(Note 12)

1

-

-

ms

PLL Clock Recovery Sample Rate Range

30

-

200

kHz

RMCK Output Jitter

(Note 14)

-

200

-

ps RMS

RMCK Output Duty Cycle

(Note 15)

45

50

55

%

OMCK Frequency

(Note 13)

1.024

-

25.600

MHz

OMCK Duty Cycle

(Note 13)

40

50

60

%

DAC_SCLK, ADC_SCLK Duty Cycle

45

50

55

%

DAC_LRCK, ADC_LRCK Duty Cycle

45

50

55

%

Master Mode

RMCK to DAC_SCLK, ADC_SCLK active edge delay

t

smd

0

-

15

ns

RMCK to DAC_LRCK, ADC_LRCK delay

t

lmd

0

-

15

ns

Slave Mode

DAC_SCLK, ADC_SCLK Falling Edge to ADC_SDOUT,

ADC_SDOUT Output Valid

t

dpd

-

ns

DAC_LRCK, ADC_LRCK Edge to MSB Valid

t

lrpd

-

26.5

ns

DAC_SDIN Setup Time Before DAC_SCLK Rising Edge

t

ds

10

-

-

ns

DAC_SDIN Hold Time After DAC_SCLK Rising Edge

t

dh

30

-

-

ns

DAC_SCLK, ADC_SCLK High Time

t

sckh

20

-

-

ns

DAC_SCLK, ADC_SCLK Low Time

t

sckl

20

-

-

ns

DAC_SCLK, ADC_SCLK falling to DAC_LRCK, SAI_LRCK

Edge

t

lrck

-25

-

+25

ns

DAC_SCLK

ADC_SCLK

(output)

RMCK

t smd

t

lmd

DAC_LRCK

ADC_LRCK

(output)

sckh

sckl

t

t

MSB

MSB-1

tdpd

ADC_SDOUT

DAC_SDINx

dh

t

ds

t

lrpd

t

lrcks

t

lrckd

t

DAC_SCLK

ADC_SCLK

(input)

DAC_LRCK

ADC_LRCK

(input)

Figure 1. Serial Audio Port Master Mode Timing

Figure 2. Serial Audio Port Slave Mode Timing