Pci bus masters, I²c bus, Sm bus – Ampro Corporation COM 830 User Manual

Page 58

Chapter 3

Signals and Pinout Tables

52

Reference Manual

COM 830

PCI Bus Masters

The COM 830 supports 4 external PCI Bus Masters. There are no limitations in connecting bus master PCI

devices.

I²C Bus

There are no onboard resources connected to the I²C bus. Address 16h is reserved for Battery Management

solutions.

SM Bus

System Management (SM) bus signals are connected to the Intel® I/O Controller Hub 82801GHM

(ICH7M-DH) and the SM bus is not intended to be used by off-board non-system management devices. For

more information about this subject please contact Ampro technical support.

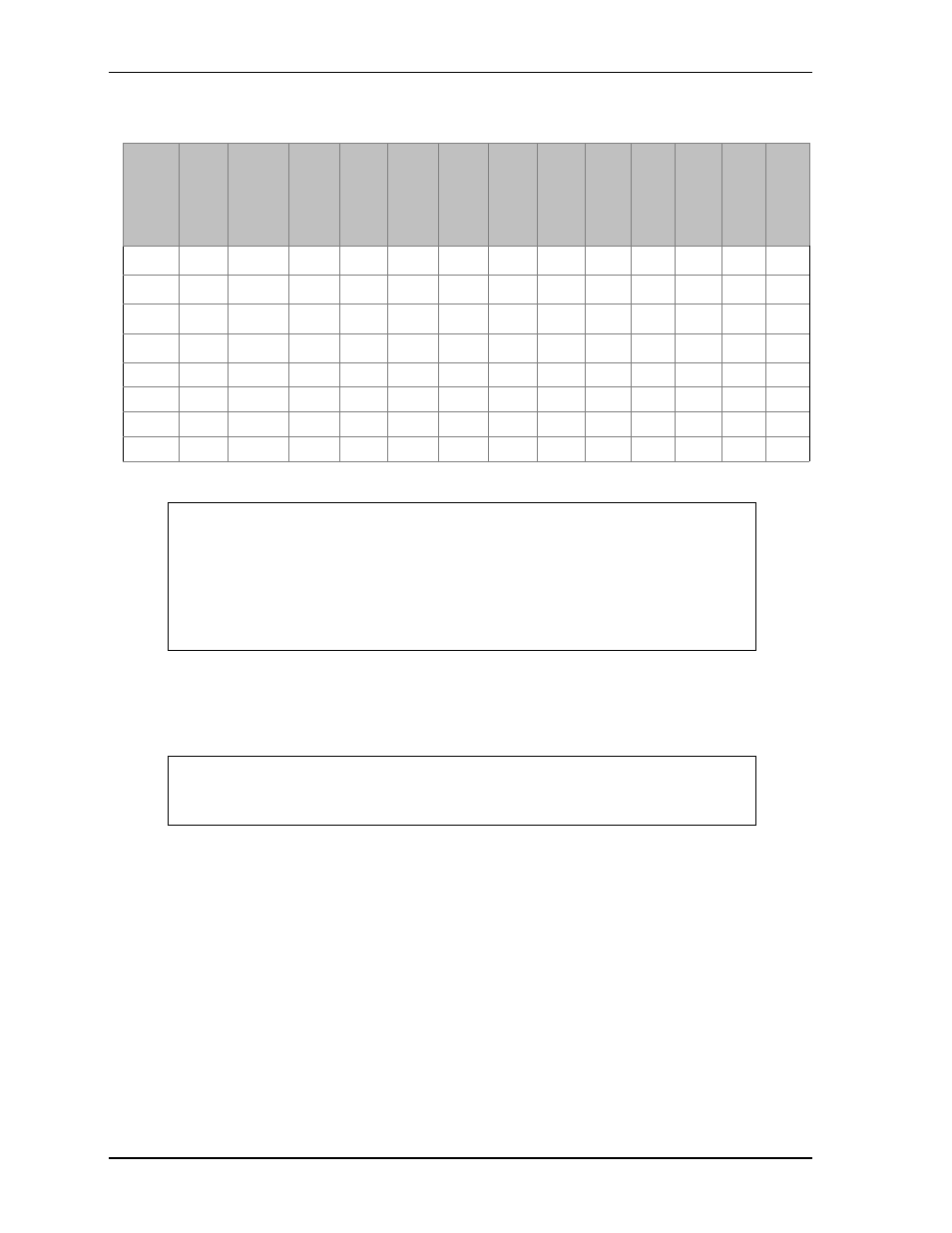

Table 3-31. PCI Interrupt Routing Map (continued)

PIRQ

Table

3-32.

LAN

SATA

Native

PCI-

EX

Root

Port

0

PCI-

EX

Root

Port

1

PCI-

EX

Root

Port

2

PCI-

EX

Root

Port

3

PCI-

EX

Root

Port

4

PCI-

EX

Root

Port

5

PCI

-EX

Port

0

PCI

-EX

Por

t 1

PCI

-EX

Port

2

PCI

-EX

Por

t 3

PCI

-EX

Por

t 4

A

x

x

x ²

x

5

x

4

x

3

x ²

B

x

x

x

x ³

x

2

x

5

x

4

x ³

C

x

x

4

x

3

x ²

x

5

x

4

D

x

x

x

5

x

4

x ³

x

2

x

5

E

F

G

H

NOTE

¹ These interrupts are available for external devices/slots on the X1 connector.

² Interrupt used by single function PCI Express devices (INTA).

³ Interrupt used by multifunction PCI Express devices (INTB).

4

Interrupt used by multifunction PCI Express devices (INTC).

5

Interrupt used by multifunction PCI Express devices (INTD).

NOTE

If there are two devices connected to the same PCI REQ/GNT pair and they are

transferring data at the same time then the latency time of these shared PCI

devices can not be guaranteed.