Ampro Corporation COM 830 User Manual

Page 47

Chapter 3

Signals and Pinout Tables

COM 830

Reference Manual

41

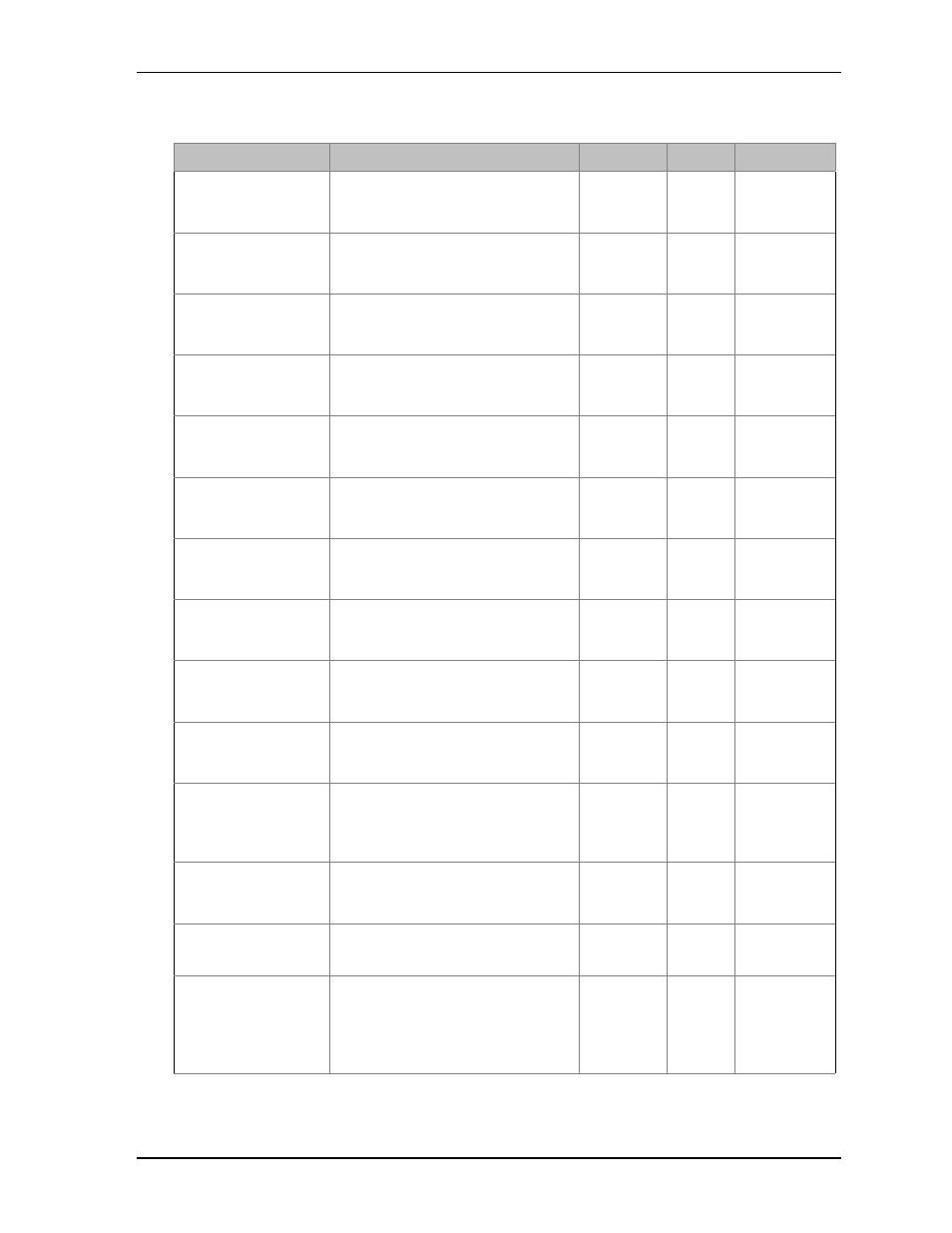

Table 3-20. SDVO Signal Descriptions

Signal

Description

I/O

PU/PD

Comment

SDVOB_RED+

SDVOB_RED-

Serial Digital Video B red output

differential pair Multiplexed with

PEG_TX[0]+ and PEG_TX[0]- pair

O PCIE

SDVOB_GRN+

SDVOB_GRN-

Serial Digital Video B green output

differential pair Multiplexed with

PEG_TX[1]+ and PEG_TX[1]-

O PCIE

SDVOB_BLU+

SDVOB_BLU-

Serial Digital Video B blue output

differential pair Multiplexed with

PEG_TX[2]+ and PEG_TX[2]-

O PCIE

SDVOB_CK+

SDVOB_CK-

Serial Digital Video B clock output

differential pair. Multiplexed with

PEG_TX[3]+ and PEG_TX[3]-

O PCIE

SDVOB_INT+

SDVOB_INT-

Serial Digital Video B interrupt input

differential pair. Multiplexed with

PEG_RX[1]+ and PEG_RX[1]-

I PCIE

SDVOC_RED+

SDVOC_RED-

Serial Digital Video C red output

differential pair. Multiplexed with

PEG_TX[4]+ and PEG_TX[4]-

O PCIE

SDVOC_GRN+

SDVOC_GRN-

Serial Digital Video C green output

differential pair. Multiplexed with

PEG_TX[5]+ and PEG_TX[5]-

O PCIE

SDVOC_BLU+

SDVOC_BLU-

Serial Digital Video C blue output

differential pair. Multiplexed with

PEG_TX[6]+ and PEG_TX[6]-

O PCIE

SDVOC_CK+

SDVOC_CK-

Serial Digital Video C clock output

differential pair. Multiplexed with

PEG_TX[7]+ and PEG_TX[7]-

O PCIE

SDVOC_INT+

SDVOC_INT-

Serial Digital Video C interrupt input

differential pair. Multiplexed with

PEG_RX[5]+ and PEG_RX[5]-

I PCIE

SDVO_TVCLKIN+

SDVO_TVCLKIN-

Serial Digital Video TVOUT

synchronization clock input

differential pair. Multiplexed with

PEG_RX[0]+ and PEG_RX[0]-

I PCIE

SDVO_FLDSTALL+

SDVO_FLDSTALL-

Serial Digital Video Field Stall input

differential pair. Multiplexed with

PEG_RX[2]+ and PEG_RX[2]-

I PCIE

SDVO_I2C_CK

(SDVO_CLK)

SDVO I²C clock line to set up SDVO

peripherals.

O 2.5V

SDVO_I2C_DAT

(SDVO_DATA)

SDVO I²C data line to set up SDVO

peripherals.

I/O OD

2.5V

SDVO_I2C_

DAT is a

boot strap

signal (see

note below)