Typical clamp configuration, Ad9883a – Analog Devices AD9883A User Manual

Page 9

REV. 0

AD9883A

–9–

GAIN

1.0

0.0

00h

FFh

INPUT RANGE – Volts

0.5

OFFSET = 00h

OFFSET = 3Fh

OFFSET = 7Fh

OFFSET = 00h

OFFSET = 7Fh

OFFSET = 3Fh

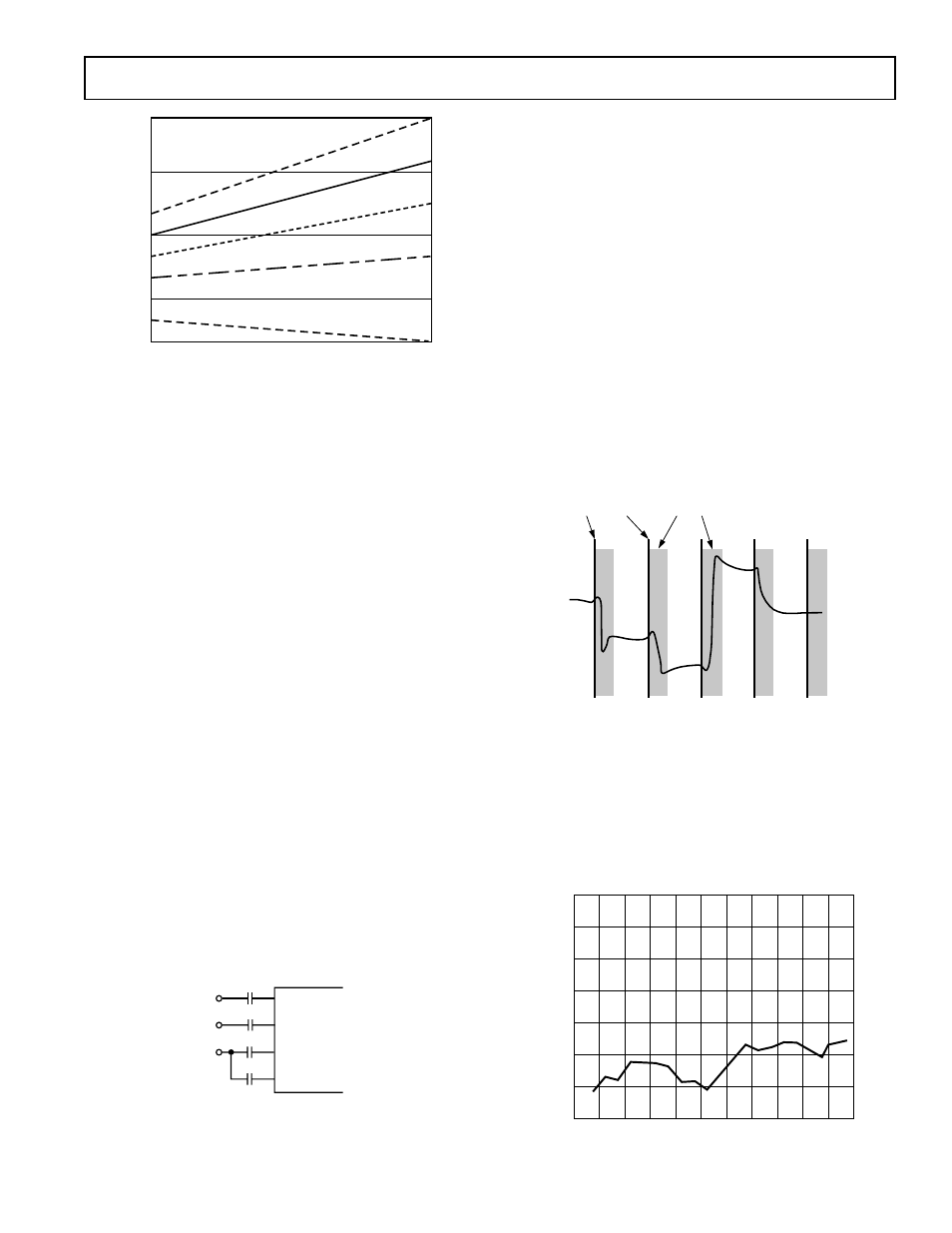

Figure 2. Gain and Offset Control

Gain and Offset Control

The AD9883A can accommodate input signals with inputs

ranging from 0.5 V to 1.0 V full scale. The full-scale range is set

in three 8-bit registers (Red Gain, Green Gain, and Blue Gain).

Note that increasing the gain setting results in an image with

less contrast.

The offset control shifts the entire input range, resulting in a

change in image brightness. Three 7-bit registers (Red Offset,

Green Offset, Blue Offset) provide independent settings for

each channel.

The offset controls provide a

±63 LSB adjustment range. This

range is connected with the full-scale range, so if the input range

is doubled (from 0.5 V to 1.0 V) then the offset step size is also

doubled (from 2 mV per step to 4 mV per step).

Figure 2 illustrates the interaction of gain and offset controls.

The magnitude of an LSB in offset adjustment is proportional

to the full-scale range, so changing the full-scale range also

changes the offset. The change is minimal if the offset setting in

near midscale. When changing the offset, the full-scale range is

not affected, but the full-scale level is shifted by the same amount

as the zero scale level.

Sync-on-Green

The Sync-on-Green input operates in two steps. First, it sets a

baseline clamp level off of the incoming video signal with a

negative peak detector. Second, it sets the sync trigger level to a

programmable level (typically 150 mV) above the negative peak.

The Sync-on-Green input must be ac-coupled to the green

analog input through its own capacitor as shown below in

Figure 3. The value of the capacitor must be 1 nF

± 20%. If

Sync-on-Green is not used, this connection is not required.

(Note: The Sync-on-Green signal is always negative polarity.)

R

AIN

B

AIN

G

AIN

SOG

47nF

47nF

47nF

1nF

Figure 3. Typical Clamp Configuration

Clock Generation

A Phase Locked Loop (PLL) is employed to generate the pixel

clock. In this PLL, the Hsync input provides a reference fre-

quency. A Voltage Controlled Oscillator (VCO) generates a

much higher pixel clock frequency. This pixel clock is divided

by the PLL divide value (registers 01H and 02H) and phase

compared with the Hsync input. Any error is used to shift the

VCO frequency and maintain lock between the two signals.

The stability of this clock is a very important element in provid-

ing the clearest and most stable image. During each pixel time,

there is a period during which the signal is slewing from the old

pixel amplitude and settling at its new value. Then there is a

time when the input voltage is stable, before the signal must

slew to a new value (Figure 4). The ratio of the slewing time to

the stable time is a function of the bandwidth of the graphics

DAC and the bandwidth of the transmission system (cable

and termination). It is also a function of the overall pixel rate.

Clearly, if the dynamic characteristics of the system remain

fixed, then the slewing and settling time is likewise fixed. This

time must be subtracted from the total pixel period, leaving the

stable period. At higher pixel frequencies, the total cycle time is

shorter, and the stable pixel time becomes shorter as well.

PIXEL CLOCK

INVALID SAMPLE TIMES

Figure 4. Pixel Sampling Times

Any jitter in the clock reduces the precision with which the

sampling time can be determined, and must also be subtracted

from the stable pixel time.

Considerable care has been taken in the design of the AD9883A’s

clock generation circuit to minimize jitter. As indicated in Fig-

ure 5, the clock jitter of the AD9883A is less than 5% of the

total pixel time in all operating modes, making the reduction

in the valid sampling time due to jitter negligible.

FREQUENCY – MHz

14

12

0

0

PIXEL CLOCK JITTER (p-p)

–

%

10

8

6

4

2

31.5

36.0 36.0 50.0 56.25

75.0 85.5

110.0

Figure 5. Pixel Clock Jitter vs. Frequency