Pinout, Ad9883a, Rev. 0 –5 – Analog Devices AD9883A User Manual

Page 5: Pin configuration, Nputs r

REV. 0

–5–

AD9883A

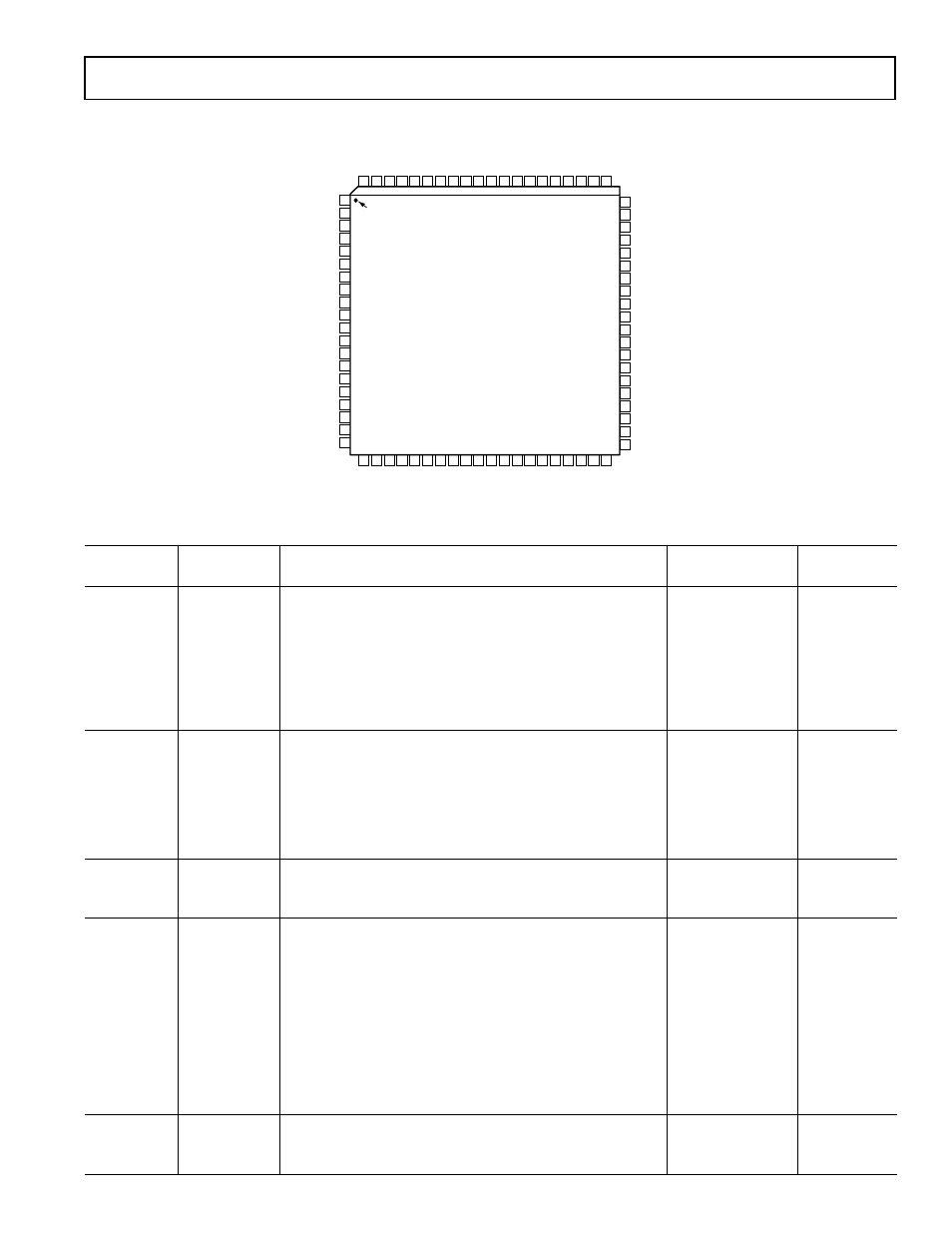

PIN CONFIGURATION

GND

GREEN <7>

GREEN <6>

GREEN <5>

GREEN <4>

GREEN <3>

GREEN <2>

GREEN <1>

GREEN <0>

GND

V

DD

BLUE <7>

BLUE <6>

BLUE <5>

BLUE <4>

BLUE <3>

BLUE <2>

BLUE <1>

BLUE <0>

GND

GND

GND

GND

GND

GND

GND

V

D

V

D

V

D

V

D

V

D

V

D

REF BYPASS

SDA

SCL

A0

R

AIN

G

AIN

B

AIN

SOGIN

80 79 78 77 76

71 70 69 68 67 66 65

75 74 73 72

64 63 62 61

1

2

3

4

5

6

7

8

9

10

11

13

14

15

16

12

17

18

20

19

21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40

PIN 1

IDENTIFIER

TOP VIEW

(Not to Scale)

AD9883A

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

GND

V

DD

V

DD

RED <0>

RED <1>

RED <2>

RED <3>

RED <4>

RED <5>

RED <6>

RED <7>

V

DD

GND

DA

T

A

C

K

HSOUT

SOGOUT

GND

V

D

GND

VSOUT

GND

V

DD

V

DD

GND

GND

V

D

PV

D

GND

MIDSCV

CLAMP

V

D

GND

CO

AST

HSYNC

VSYNC

GND

FIL

T

PV

D

V

D

GND

Table I. Complete Pinout List

Pin

Pin

Type

Mnemonic

Function

Value

Number

I

nputs

R

AIN

Analog Input for Converter R

0.0 V to 1.0 V

54

G

AIN

Analog Input for Converter G

0.0 V to 1.0 V

48

B

AIN

Analog Input for Converter B

0.0 V to 1.0 V

43

HSYNC

Horizontal SYNC Input

3.3 V CMOS

30

VSYNC

Vertical SYNC Input

3.3 V CMOS

31

SOGIN

Input for Sync-on-Green

0.0 V to 1.0 V

49

CLAMP

Clamp Input (External CLAMP Signal)

3.3 V CMOS

38

COAST

PLL COAST Signal Input

3.3 V CMOS

29

Outputs

Red [7:0]

Outputs of Converter “Red,” Bit 7 is the MSB

3.3 V CMOS

70–77

Green [7:0]

Outputs of Converter “Green,” Bit 7 is the MSB

3.3 V CMOS

2–9

Blue [7:0]

Outputs of Converter “Blue,” Bit 7 is the MSB

3.3 V CMOS

12–19

DATACK

Data Output Clock

3.3 V CMOS

67

HSOUT

HSYNC Output (Phase-Aligned with DATACK)

3.3 V CMOS

66

VSOUT

VSYNC Output (Phase-Aligned with DATACK)

3.3 V CMOS

64

SOGOUT

Sync on Green Slicer Output

3.3 V CMOS

65

References

REF BYPASS

Internal Reference Bypass

1.25 V

58

MIDSCV

Internal Midscale Voltage Bypass

37

FILT

Connection for External Filter Components for Internal PLL

33

Power Supply

V

D

Analog Power Supply

3.3 V

26, 27, 39, 42,

45, 46, 51, 52,

59, 62

V

DD

Output Power Supply

3.3 V

11, 22, 23, 69,

78, 79

PV

D

PLL Power Supply

3.3 V

34, 35

GND

Ground

0 V

1, 10, 20, 21,

24, 25, 28, 32,

36, 40, 41, 44,

47, 50, 53, 60,

61, 63, 68, 80

Control

SDA

Serial Port Data I/O

3.3 V CMOS

57

SCL

Serial Port Data Clock (100 kHz Maximum)

3.3 V CMOS

56

A0

Serial Port Address Input 1

3.3 V CMOS

55