GW Instek GFC-8010H User Manual

Page 8

FREQUENCY COUNTER

USER MANUAL

13

6. CIRCUIT DESCRIPTION

6-1. Theory of Operation

In order to get the most benefit from the frequency counter, it’s useful to

comprehend the circuit thoroughly. We have attempted every possible to

utilize the latest developments in large-scale integration to provide the

greatest performance for the money and, at the same time, to reduce the

complexity of circuit and increase reliability.

Ignoring the prescaler for the moment, let us assume the input signal

arrives at the 10MHz to 100MHz input labeled CHA in main board. This

signal is first amplified by the Q201~Q202 pair. The three amplifier

stages identified as U202 in the schematic are ECL logic stages biased in

its linear region, each stage having a gain before feedback of about 5. A

positive feedback at the output of the third amplifier when reflected

through the gain of the proceeding three amplifier states (including the

Q201~Q202 pair) results in about a 5mV hysteresis in the input triggering

levels to aid in noise rejection. Q203 and Q204 translate the ECL levels to

TTL levels. The signal is presented directly to the counter IC U301.

The IC U301 provides all the functions of the counter and display result

through LED.

U201 regulates the input 9 volts signal from the line voltage transformer

and rectifier circuit. When the power switch is set to “on” position,

approximately 5.0 volts is applied to the circuit.

FREQUENCY COUNTER

USER MANUAL

14

6-2. Frequency Measurement Accuracy

Measurement Accuracy

Frequency measurement accuracy is determined by the following two

conditions:

1) ±1count.

2) Time base accuracy.

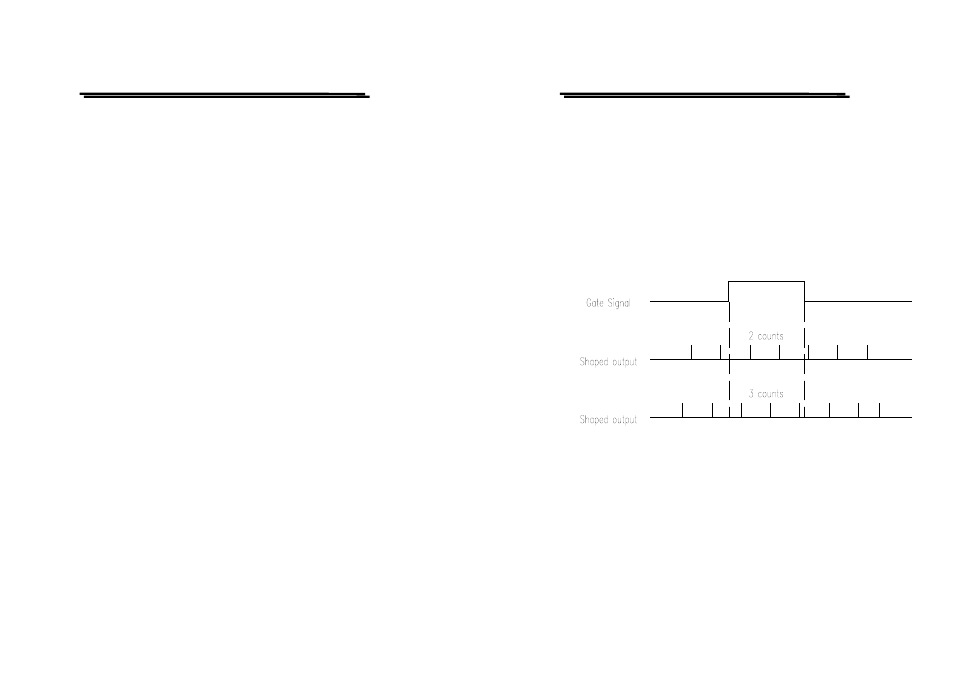

The ±1 count error is inherent to digital meters and is produced by the

phase relationship between the gate signal and the input signal shown in

Fig. 7. The counted result of 1 count increased or decreased depends on

the phase difference.

Fig. 7 ±1 count error