Clock recovery theory – Teledyne LeCroy SDA III-CompleteLinQ User Manual

Page 25

Operator's Manual

this relationship is f

c

= 2.06 f

n

. Settings for the Custom PLL: Touch inside the Poles field to select the

order of the PLL. The number of poles can be 1 or 2.

Clock Recovery Theory

Eye, jitter and vertical noise analysis all require a clock that defines the boundaries of each unit interval.

Additionally, the clock is used to determine the difference between actual and expected arrival times of

data edges (i.e., the time interval error, or TIE measurements). In many of today's high-speed serial stand-

ards, the clock is not a physical signal but is instead derived from the data signal via clock recovery hard-

ware or software. SDAIII-CompleteLinQ includes a clock recovery algorithm that determines the clock

from the either the data signal or from an explicit clock signal.

You may use a PLL as part of the clock recovery algorithm in order to best emulate the PLL in a receiver.

The recovered clock is defined by a list of times that correspond to expected edge arrival times.

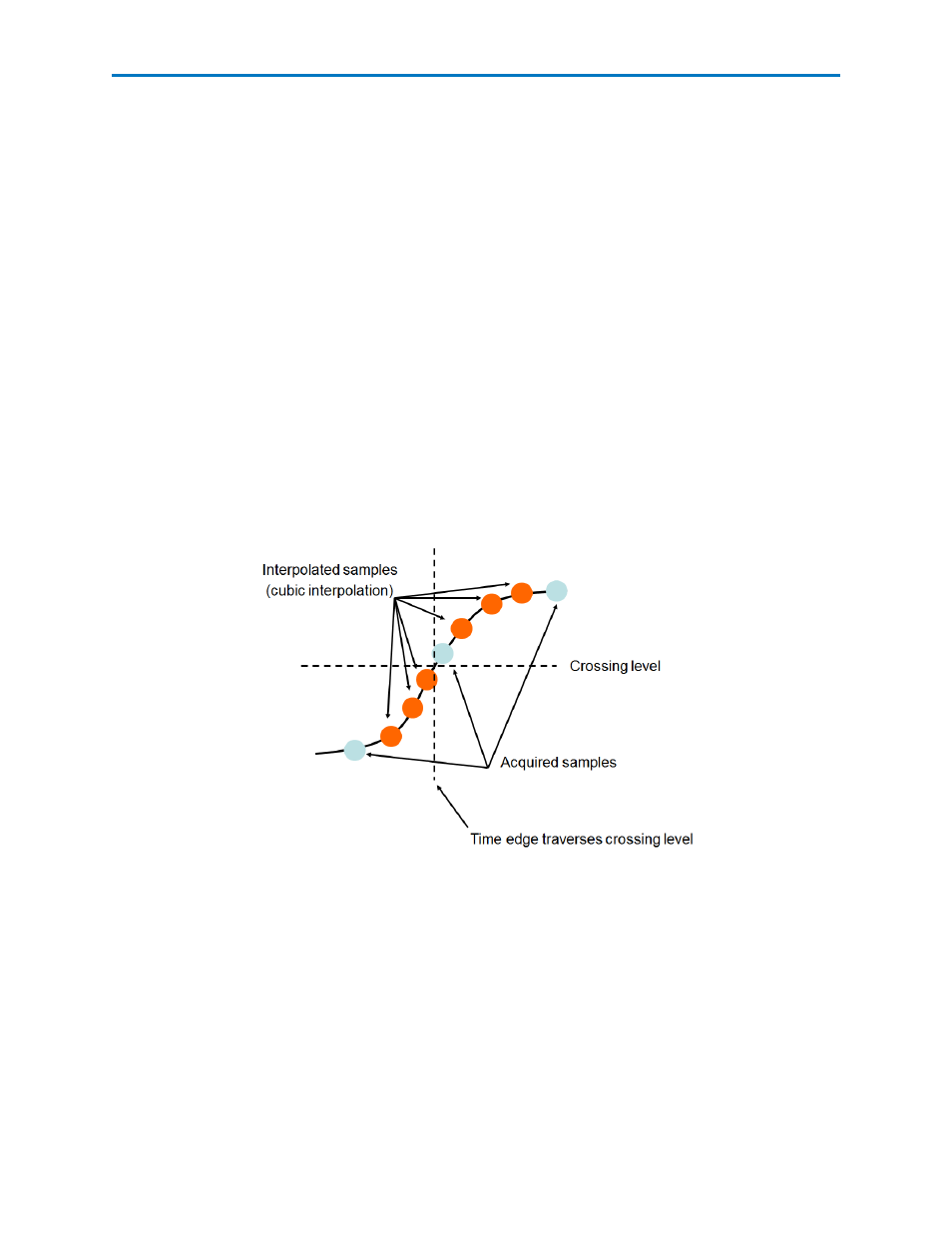

The first step in creating a clock signal that is tracked by a PLL is to create a digital phase detector. This is

simply a software component that measures the location in time when a signal crosses a given threshold

value. Even given the maximum sampling rate available), interpolation is necessary in order to accurately

determine crossing times. Interpolation is automatically performed by SDAIII-CompleteLinQ. Inter-

polation is not performed on the entire waveform; rather, only the points surrounding the crossing level

are interpolated. A cubic interpolation is used, followed by a linear fit to the interpolated data to find the

precise time that a data signal edge traverses the crossing level (see figure below).

SDA Edge Time Determination

Clock recovery implementation in the SDA is shown in the following figure. This algorithm generates time

values corresponding to a clock at the data rate. The computation follows variations in the data stream

being tested through the use of a feedback control loop correcting each period of the clock by adding a

portion of the error between the recovered clock edge and the nearest data edge.

921143 Rev A

23