Atec Anritsu-MG3670 Series User Manual

Page 9

RADIO COMMUNICATIONS, EMI MEASURING TEST INSTRUMENTS

298

www.anritsu.com

For product ordering information, see pages 4-7.

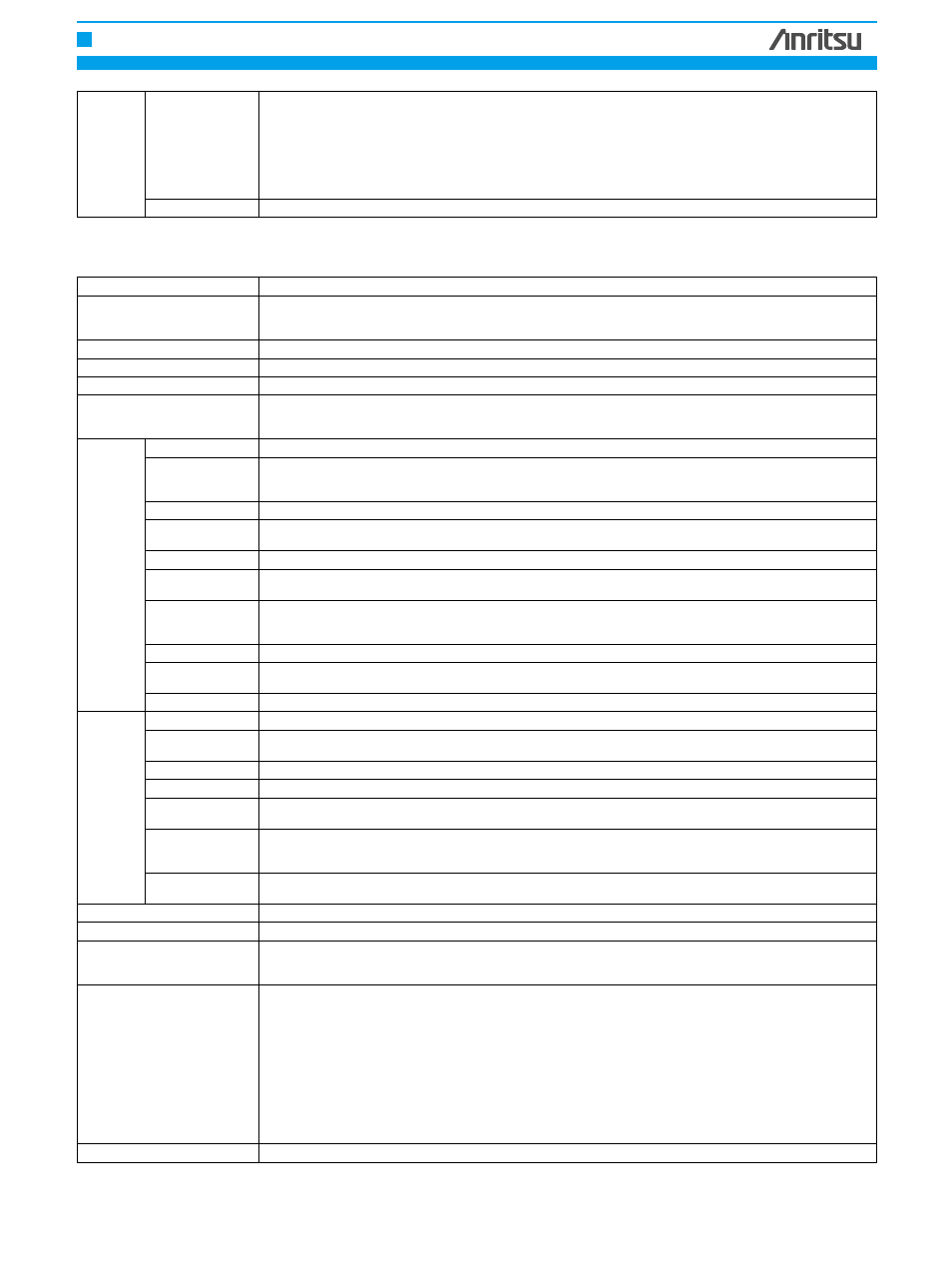

Carrier frequency range

4 kHz to 2250 MHz (MG3670B/C), 4 kHz to 2750 MHz (MG3671A/B and MG3672A)

–143 to +8 dBm, 0.1 dB steps (1 channel only on, PCB MUX must be off when traffic present)

RF output level

–143 to +4 dBm, 0.1 dB steps (multiplex channel)

Frequency response, level accuracy: Depends on main frame (after level calibration)

Supported systems

IS-95: US Digital Cellular System

Modulation format

Forward link: SS + QPSK; Reverse link: SS + OQPSK

Chip rate

1.2288 Mcps

IS-95 recommended filters: SPEC 1, SPEC 2, SPEC 3, SPEC 1 + EQ, SPEC 2 + EQ, SPEC 3 + EQ

Baseband filters

Nyquist filters:

α = 0.2, 0.25, 0.3, 0.35, 0.4, 0.45, 0.5

Root Nyquist filters:

α = 0.2, 0.25, 0.3, 0.35, 0.4, 0.45, 0.5

Multiplex channels

Channels 1 to 5

CH 1: Current Pilot, Off

Supported channels

CH 2 to CH 5: Nth Pilot, Sync, Paging, Traffic, OCNS, Off

(Sync available for 1 selected channel only, all channels cannot be turned off simultaneously.)

Spread code

Walsh code + Short code

Point: 0, Sync: 32, Paging: 1 to 7, Traffic: 8 to 31/33 to 63, OCNS: 0 to 63

Walsh code

(Except for Pilot code, same code number cannot be set for multiple channels.)

Forward

Short code offset

0 to 3276 chips in 64 chip steps (for Current Pilot), 1 chip steps (for Nth Pilot)

link

Sync 1200 bps, Paging: 4800/9600 bps, OCNS: 19200 sps, Traffic: 1200/2400/4800/9600 bps,

Data rate

1800/3600/7200/14400 bps (Single channel selection only, except for 9600/14400 bps)

(RF output level + upper limit for each no. of multiplex channels) to –20 dB in 0.1 dB steps

Channel level

Upper limit for each no. of multiplex channels: –3 dB (2 channels), –5 dB (3 channels), –6 dB (4 channels), –7 dB (5 channels)

*

Level is set automatically for channel with highest CH number, user setting not possible.

Scramble function

Long code scramble on/off (for Paging/Traffic/OCNS)

Power control bit transmission on/off (for Traffic)

PCB MUX function

PCB data: Selectable 256 bit data repeating pattern

Long code mask

42 bits can be set by user in each channel (scramble On, PCB MUX On)

Multiplex channels

Channels 1 to 4

CH 1: Traffic, Access, Interfered

Supported channels

CH 2 to CH 4: Traffic, Access, Interfered, Off

Spread code

Long code + short code

Long code mask

42 bits can be set by user in each channel.

Reverse

Access: 4800 bps, Interfered: 28800 sps

link

Data rates

Traffic: 1200/2400/4800/9600 bps, 1800/3600/7200/14400 bps (For CH1 only on, except for 9600/14400 bps)

(RF output level + upper limit for each no. of multiplex channels) to –15 dB in 0.1 dB steps,

Channel level

Upper limit for each No. of multiplex channels: 0 dB (2 channels), 2 dB (3 channels), –3 dB (4 channels)

CH 1 is fixed on upper limit, user setting not possible.

Power monitor

CH 1 to CH 4 composite output level, CH 2 to CH 4 composite output level (N), S/N ratio of CH 1 output level (S),

function

CH 1 Eb/N (Multiplex channel only)

Frame offset

0 to 15 power control group (PCG) in 1 PCG steps

Internal frame structure

Frame formats for all channel types specified by IS-95

Pseudo-random patterns: PN7, PN9, PN15

Internal modulation data

Fixed pattern: User settable 16 bit data repeating pattern

Sequence data: User can set sequence data in internal RAM (2048 bits x 7 blocks) as repeating pattern of 1 to 8192 frames.

Using internal time reference clock

Data Clock: Data rate clock synched to Ref Clock and Frame Clock

Data: Digital data synched to Data Clock

ESTM Clock: 0.5 pulse/s clock synched to Ref Clock and Data Clock

Frame Clock: Channel frame clock synched to Ref Clock and ESTM Clock

External modulation data

BNC connector, TTL level, polarity switchable

Using external time reference clock

Ref Clock: ±2% of 19.6608, 9.8304, 4.9152, 2.4576 or 1.2288 MHz

Data: Digital data synched to Data Clock

ESTM Clock: 0.5 pulse/s clock synched to Ref Clock and Data Clock

Frame Clock: Channel frame clock synched to Ref Clock and ESTM Clock

BNC connector, TTL level, polarity switchable

I/Q signal output

50

Ω or CMOS (600 Ω), BNC connector

V + D mode: Downlink NORMAL; Any SB, SSB, NTS field data

SYNC; Any FC, SSB1, STS, SBB, SB2 field data

Uplink

NORMAL; Any SB, NTS field data

Edit function

CONTROL; Any SCB, ETS field data

TETRA

PDO mode: Downlink SYNC; Any FC, SB, STS field data

NORMAL; Any SB, NTS field data

Uplink

START; Any ETS, SB field data, R bit Length

EVEN; Any NTS field data

Scramble function

Any scramble code setting

*

1: The pseudorandom pattern in each slot has a different phase, and its pattern is continuous within the data field of slots.

*

2: Applicable when this unit is installed in MG3670B/C, MG3671A/B, and MG3672A. Not applicable when this unit is installed in MG3670A.

MG0310A CDMA Modulation Unit (incorporated in the MG3670B/C, MG3671A/B and MG3672A)*

1

Continued on next page