Atec Anritsu-MG3670 Series User Manual

Page 7

RADIO COMMUNICATIONS, EMI MEASURING TEST INSTRUMENTS

296

www.anritsu.com

For product ordering information, see pages 4-7.

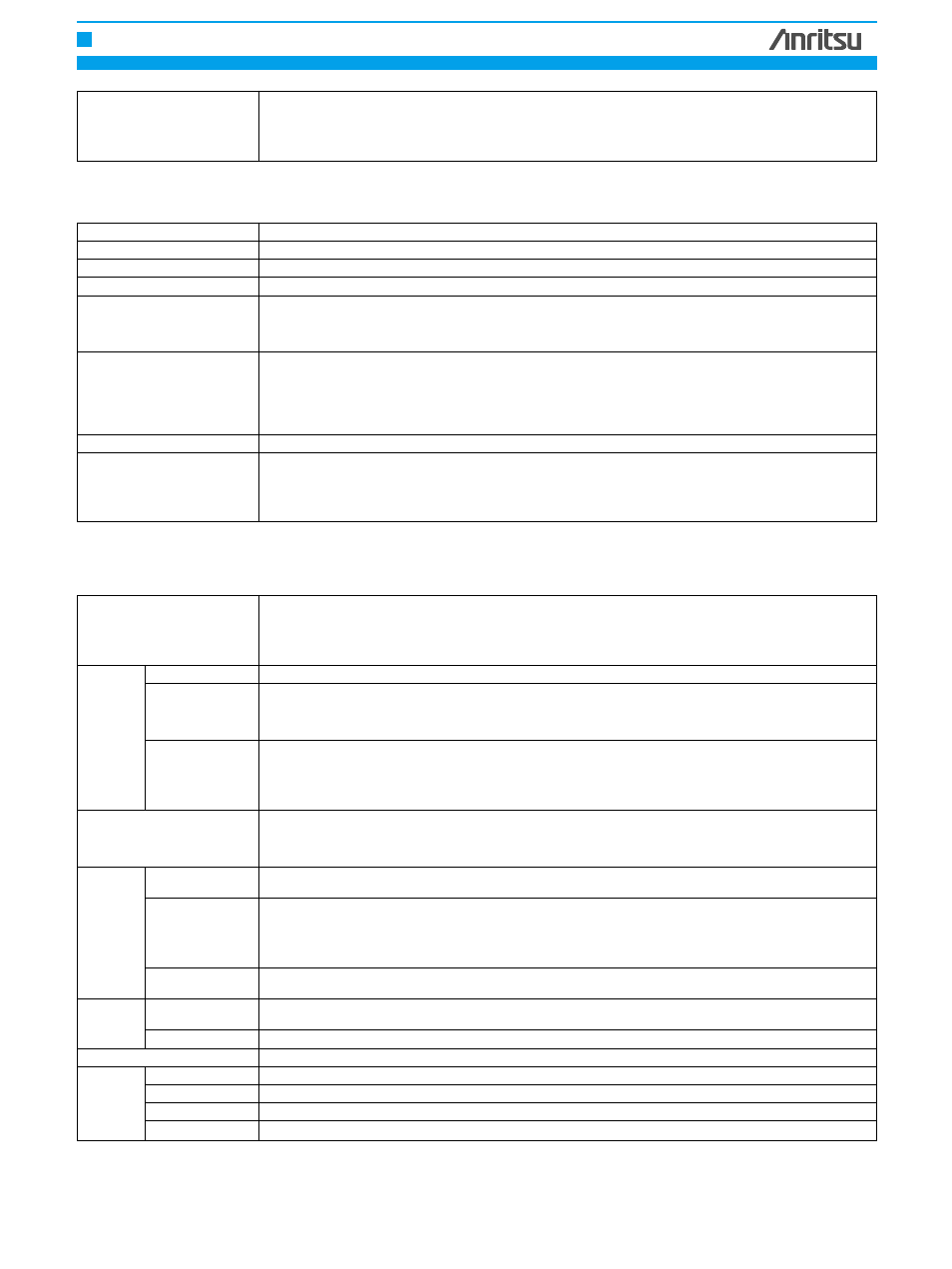

PDC, PDC_H, PHS, NADC, TFTS (with MG0301C)

GSM, PCN (DCS1800), CT2 (with MG0302A)

Applicable communication system

DECT (with MG0305A)

PACS, WCPE, PHS (with MG0307A)

TETRA (with MG0311A)

Internal data mode

TDMA framing specified for each system; modulation in each time slot using any internal modulation data

Pseudo-random pattern: PN15/PN9*

1

(for device)

Internal data

Specified pattern based on communication channel format specified for each system:

Up/down communication channel, VOX signal control

Modulation

TCH section consists of pseudo-random pattern PN15/PN9*

1

signal

DATA CLOCK: Covering ±5% of bit rate

DATA: Digital data synchronized with DATA CLOCK

External data mode

SYMBOL CLOCK: Clock specified by DATA synchronized with DATA CLOCK

BURST GATE: Burst signal synchronized with DATA CLOCK (on:

≥14 symbols, off: ≥8 symbols)

TTL level, BNC connector, polarity selectable

Burst wave output synchronized with trigger input signal of burst repetition rate (frame cycle) at internal modulation

Burst trigger input

Input period:

≤burst repetition rate ±1 symbol [PDC, PDC_H, PHS, NADC, GSM, PCN (DCS1800), CT2, DECT, PACS,

WCPE, TETRA],

≤burst repetition rate ±1/2 symbol (TFTS)

TTL level, BNC connector (rear panel), polarity selectable

Burst trigger output

Outputs 1-symbol wide pulse at same cycle as burst waveform output at internal modulation

TTL level, BNC connector (rear panel), polarity selectable

Following outputs selectable at internal modulation

Control

PN CLOCK: Data clock corresponding to pseudo-random pattern part

signal

Pattern sync output

PN GATE: Gate signal corresponding to pseudo-random pattern part

output

RF GATE: Signal for controlling pulse modulator in accordance with burst signal output

TTL level, BNC connector (rear panel)

Burst gate output

Outputs gate signal corresponding to burst waveform output at internal modulation

TTL level, BNC connector (rear panel), polarity selectable

Burst on/off ratio

≥80 dB (+5 dBm output, PDC, PDC_H, NADC, CT2, TFTS, TETRA), ≥75 dB (+5 dBm output, PHS, GSM, PCN, PACS),

RF output

≥70 dB (+5 dBm output, DECT, WCPE)

Rise/fall time

Equivalent to 2 symbols

Memory (pattern memory)

Max. 100 patterns/system (save and recall of internal modulation pattern data)

Burst repetition rate

20 ms

NADC

Slot configuration

For device, up/down communication channel

Output slot select

On/off selectable for any slots of slot 0 to slot 2 (excluding all slots off)

Edit function

SYNC/SACCH/CDVCC: Any data, DATA: PN9, PN15*

1

selectable

Carrier frequency range:

1 to 2250 MHz*

1

(incorporated in the MG3670B/C), 1 to 2750 MHz (incorporated in the MG3671A/B and MG3672A)

PHS

Bit rate: 384 kbps

Baseband filter: Root Nyquist (

α = 0.5), Nyquist (α = 0.5)

Adjacent channel power ratio:

≤–74 dB (600/900 kHz offset, ±96 kHz band, ≥10 MHz)*

2

*

1: The upper frequency is limited by the specifications of the mainframe in which this unit is installed.

*

2: Applicable when this unit is installed in MG3670B/C, MG3671A/B and MG3672A. Not applicable when this unit is installed in MG3670A.

MG0311A

π/4 DQPSK Modulation Unit (incorporated in MG3670B/C, MG3671A/B and MG3672A)

Applicable communication system

TETRA

Modulation system

π/4 DQPSK

Vector error

I/Q signal:

≤1.5%rms (at 50 Ω output); RF signal: ≤1.8%rms (at ≤+5 dBm output)

Internal modulation data

Pseudo-random pattern: PN15/PN9, Free 4-bit repetition pattern (ex: 0101, 0011)

DATA CLOCK: Covering ±5% of bit rate

External modulation data

DATA: Digital data synchronized with DATA CLOCK

SYMBOL CLOCK: Clock specified by DATA synchronized with DATA CLOCK

*

TTL level, BNC connector, polarity selectable

Selectable 50

Ω or CMOS (600 Ω), BNC connector

50

Ω setting (modulation data: 0000): 1 Vp-p ±5% (MG3670A/B/C, MG3671A/B), 2 Vp-p ±5% (MG3672A)

I/Q signal output

CMOS setting (modulation data: 0000)

Variable in 10% steps over range of 10% to 100% of 1 Vp-p ±5%, variable offset voltage: 0 to 4 V in 1 mV steps

(MG3670A/B/C, MG3671A/B), Variable in 10% steps over range of 10% to 100% of 2 Vp-p ±5%, variable offset voltage:

0 to 4 V in 1 mV steps (MG3672A)

Phase encode function

Invertible phase change polarity at modulation

Carrier frequency range:

300 kHz to 2250 MHz*

1

(incorporated in MG3670B/C), 300 kHz to 2750 MHz (incorporated in MG3671A/B and MG3672A)

TETRA

Bit rate: 36 kbps

Baseband filter: Root Nyquist (

α = 0.35), Nyquist (α = 0.35)

Adjacent channel leakage power ratio*

2

:

≤–48 dB (25 kHz offset, ±9 kHz band), ≤–67 dB (50 kHz offset, ±9 kHz band)

*

1: The upper frequency is limited by the specifications of the mainframe in which this unit is installed.

*

2: Also applicable when this unit is installed in the MG3670A with option 11 (low adjustment channel leakage power). This unit can not be installed in the

MG3670A without option 11.

MG0303B Burst Function Unit (incorporated in the MG3670B/C, MG3671A/B and MG3672A)

Continued on next page