Atec Anritsu-MG3670 Series User Manual

Page 11

RADIO COMMUNICATIONS, EMI MEASURING TEST INSTRUMENTS

300

www.anritsu.com

For product ordering information, see pages 4-7.

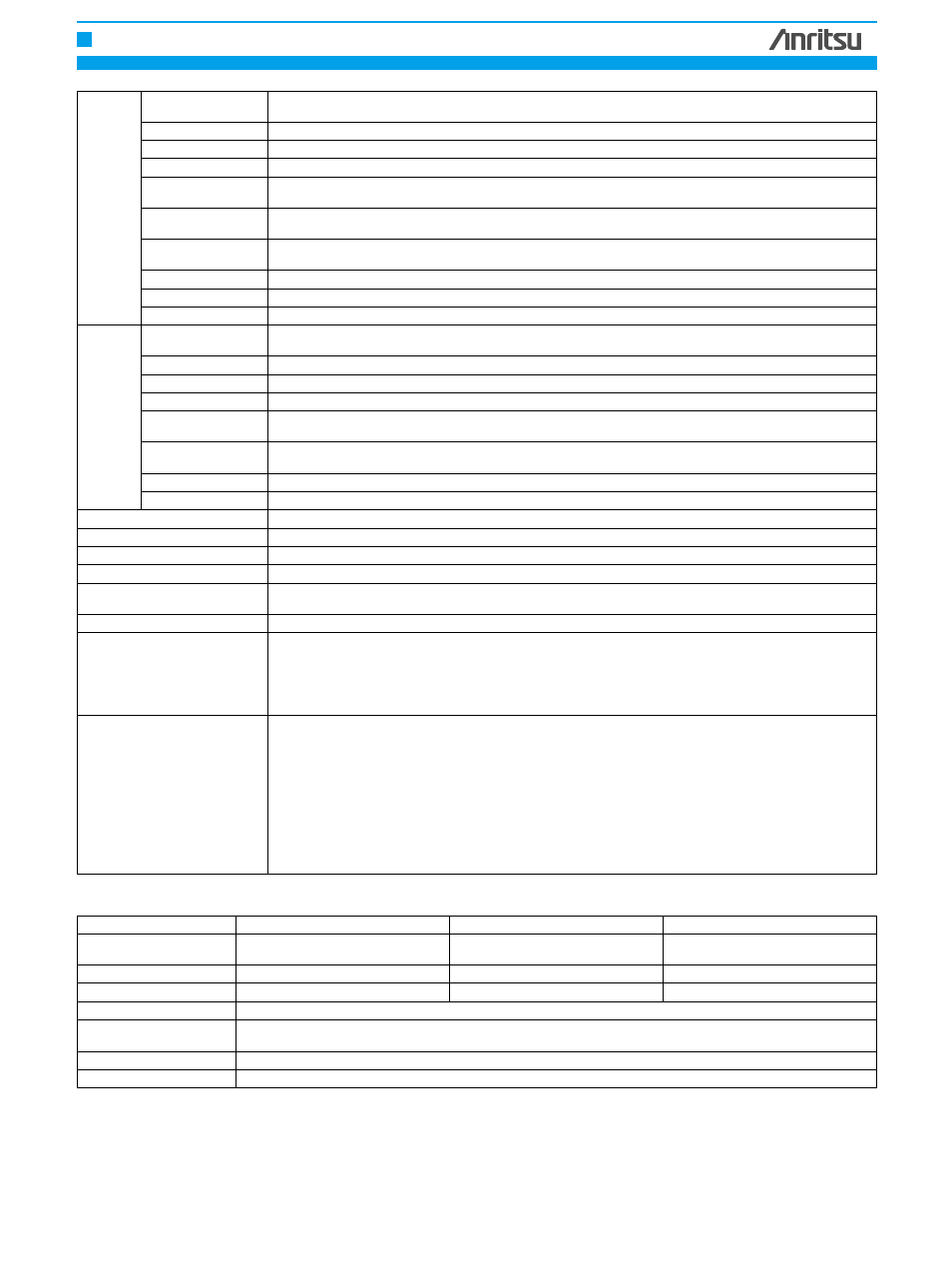

Number of multiplex

Settable channels: 8

channels

Maximum multiplex: 56 (limited to output level, used at Other Channel function)

Supported channels

PERCH 1, PERCH 2, CONTROL, DTCH

Spread code

Long code: Gold code, Short code: Layered orthogonal code sequence

Channel level

0.0 to –20.0 dB (0.1 dB steps; Maximum value varies with multiplex)

Long code setting

Down link

range

00000H to 3FFFFH (initial phase variable function)

Short code for long

00H to FFH

code masked symbols

Short code setting

range

4 to 256 chip length

Encoder function

CRC encoder, convolution encoder, interleaver

P-down function

Variable long code masked symbol (0 to –20 dB, 0.1 dB steps)

Symbol rate

16 to 1024 ksps

Number of multiplex

Any settable channel: 8, Maximum multiplex: 8

channels

Supported channels

DTCH

Spread code

Long code: Gold code, Short code: Layered orthogonal code sequence

Channel level

0.0 to –20.0 dB (0.1 dB steps; Maximum value varies with multiplex)

Up link

Long code setting

range

00000000000H to 1FFFFFFFFFFH

Short code setting

range

4 to 256 chip length

Encoder function

CRC encoder, convolution encoder, interleaver

Symbol rate

16 to 1024 ksps

Frame offset

0 to 15 slot

Internal frame structure

BCCH, FACH-L, DTCH, ACCH

I/Q signal output

50

Ω and CMOS (600 Ω) selectable, BNC connector

Vector error

EVM:

≤5.0%rms (filter mode: EVM, output: 0 dBm, only 1 channel on, level control program function: off)

≤–63 dBc (specification value), ≤–65 dBc (typical)

Spurious emissions

*

5 MHz offset, 0 dBm output, only 1 channel on, 18˚ to 30˚C, 1.8 to 2.2 GHz, filter mode: ACP

Level control program function

Level control resolution: 1.0 dB, Time resolution: 0.625 ms

Front panel

DATA: Input data for User CH set at External Input Channel

Auxiliary inputs

TIMING CLOCK: Clock synchronized to super frame

(TTL level, BNC connector)

DATA CLOCK: Input data clock set at External Input channel

Rear panel

LONG CODE TRIGGER: Long code start trigger signal

Rear panel

DATA: Data for User CH set at External Output Channel (switchable using Data Select to data before and after spread)

DATA CLOCK: Data clock corresponding to each channel setting (switchable using Data Select to Symbol or Chip use)

TIMING CLOCK: Clock synchronized to super frame

FRAME CLOCK: Clock synchronized to radio frame

Auxiliary outputs

SYMBOL CLOCK: Symbol clock (switchable using Data Select to Symbol Clock and Chip Clock)

(TTL level, BNC connector)

REF CLOCK: Clock of 1, 2, 4, and 8 time chip rate

Rear panel expansion output connector

LONG CODE I: Long code for in-phase component

LONG CODE Q: Long code for orthogonal component

LONG CODE TRIGGER: Long code start trigger

SLOT CLOCK: Clock synchronized to Time slot

Model

Start-up characteristics

Aging rate

Temperature characteristic (0˚ to 50˚C)

MG3670/3671/3672 Option 01

7 x 10

–8

/day (after 30 min. warm-up)

3 x 10

–8

/day (after 60 min. warm-up)

5 x 10

–9

/day (after 24-h warm-up)

±5 x 10

–8

/day

MG3670/3671/3672 Option 02

2 x 10

–8

/day (after 60 min. warm-up)

2 x 10

–9

/day (after 24-h warm-up)

±1.5 x 10

–8

/day

MG3670/3671/3672 Option 03

–

5 x 10

–10

/day (after 48-h warm-up)

±5 x 10

–9

/day

MG3670B Option 20

RF off release function (When RF is off, level display and level setting is enabled.)

MG0301C Option 22

PHS LCCH super frame control pattern function (artificial base station signal output for field strength measurement: A PS

connection test is impossible.)

MG0302A Option 23

CT2 MUX3 control pattern function

MG3670B/3671A Option 25

Format upgrade (enables MG0310A to be used in MG3670B/3671A)

•

Options