Ap7173, Electrical characteristics – Diodes AP7173 User Manual

Page 5

AP7173

1.5A LOW DROPOUT LINEAR REGULATOR WITH

PROGRAMMABLE SOFT-START

AP7173

Document number: DS31369 Rev. 9 - 2

5 of 15

April 2011

© Diodes Incorporated

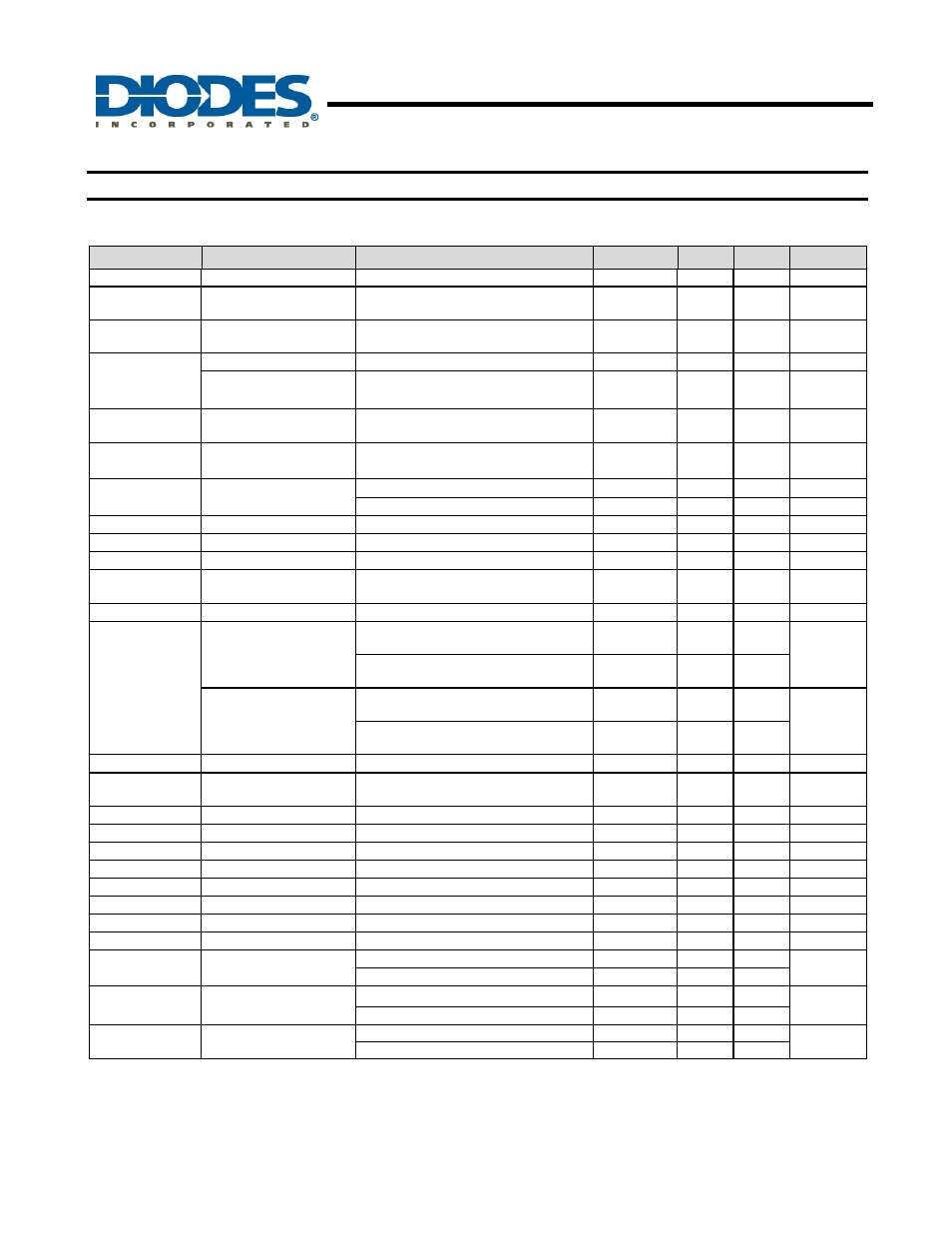

Electrical Characteristics

At V

EN

= 1.1V, V

IN

= V

OUT

+ 0.5V, C

VCC

= 0.1uF, C

IN

= C

OUT

= 10uF, I

OUT

= 50mA, V

VCC

= 5.0V, and T

A

= –40°C to +85°C,

unless otherwise noted. Typical values are at T

A

= +25°C.

Symbol

Parameter

Test Conditions

Min

Typ.

Max

Unit

V

IN

Input

Voltage

Range

V

OUT

+ V

DO

5.5

V

V

VCC

Bias Pin Voltage Range

(Note 7)

2.7

5.5

V

V

REF

Internal Reference

(Adj.)

T

A

= +25 ºC

0.792

0.8

0.808

V

V

OUT

Output Voltage Range V

IN

= 5V, I

OUT

= 1.5A

0.8

3.3

V

Accuracy (Note 8)

2.97V≤V

VCC

≤5.5V,

50mA≤I

OUT

≤1.5A

–2 ±0.5

2 %

ΔV

OUT

/

ΔV

IN

/

V

OUT

Line Regulation

V

OUT (NOM)

+ 0.5≤V

IN

,

5.5V

0.03

%/V

ΔV

OUT

/V

OUT

/

ΔI

OUT

Load Regulation

50mA≤I

OUT

≤1.5A

0.09

%/A

V

DO

Dropout Voltage

(Note 9)

I

OUT

= 1.5A,V

VCC

–V

OUT(NOM)

≥3.25V 165

270 mV

I

OUT

= 1.5A, V

IN

= V

VCC

1.5

1.7

V

I

CL

Current

Limit

V

OUT

= 80% x V

OUT (NOM)

2

3

4

A

I

SHORT

Short-Circuit

Current

V

OUT

< 0.2V

0.6

1

A

I

VCC

Bias Pin Current

1

2

mA

I

SHDN

Shutdown Supply

Current (I

GND

)

V

EN

≤0.4V

1

50

µA

I

FB

Feedback

Pin

Current

–1 0.1

1 µA

PSRR

Power-Supply Rejection

(V

IN

to V

OUT

)

1KHz, I

OUT

= 1A,

V

IN

= 1.8V, V

OUT

= 1.5V

60

dB

300KHz, I

OUT

=1A,

V

IN

= 1.8V, V

OUT

=1.5V

30

Power-SupplyRejection

(V

VCC

to V

OUT

)

1KHz, I

OUT

= 1A,

VI

N

= 1.8V, V

OUT

=1.5V

50

dB

300KHz, I

OUT

= 1A,

V

IN

= 1.8V, V

OUT

=1.5V

30

T

ST

Startup

Time

R

LOAD

for I

OUT

= 1.0A, C

SS

= open

100

µS

I

SS

Soft-Start Charging

Current

V

SS

= 0.4V

440

nA

V

EN, HI

Enable Input High Level

1.1

5.5

V

V

EN, LO

Enable Input Low Level

0

0.4

V

V

EN, HYS

Enable Pin Hysteresis

50

mV

I

EN

Enable Pin Current

V

EN

= 5V

0.1

1

µA

V

PG, TH

PG Trip Threshold

V

OUT

decreasing

85 90

94

%V

OUT

V

PG, HYS

PG

Trip

Hysteresis

3

%V

OUT

V

PG, LO

PG Output Low Voltage I

PG

= 1mA (sinking), V

OUT

PG , TH 0.3 V I PG, LKG PG Leakage Current V PG = 5.25V, V OUT >V PG , TH 0.1 1 µA T SD Thermal Shutdown Shutdown, temperature increasing +150 ºC Reset, temperature decreasing +130 θ JA Thermal Resistance DFN3030-10 (Note 10) 35 o C/W SO-8EP (Note 11) 23 θ JC Thermal Resistance DFN3030-10 (Note 10) 4.9 o C/W SO-8EP (Note 11) 1.8 Notes: 7. V VCC should be higher or equal to V IN in this chip. 8. Tested at 0.8V; resistor tolerance is not taken into account. 9. Dropout is defined as the voltage from V IN to V OUT when V OUT is 3% below nominal. 10. Test condition for DFN3030-10: Device mounted on FR-4 substrate (2s2p), 2"*2" PCB, with 2oz copper trace thickness and large pad pattern. 11. Test condition for SOP-8L-EP: Device mounted on FR-4 substrate (2s2p), 2"*2" PCB, with 2oz copper trace thickness and large pad pattern.

Temperature

Junction-to-Ambient

Junction-to-Case