12v microtlynx, 12a: non-isolated dc-dc power modules, Data sheet – GE Industrial Solutions 12V MicroTLynx 12A User Manual

Page 17

GE

Data Sheet

12V MicroTLynx

TM

12A: Non-Isolated DC-DC Power Modules

4.5Vdc –14Vdc input; 0.69Vdc to 5.5Vdc output; 12A Output Current

May 2, 2013

©2013 General Electric Company. All rights reserved.

Page 17

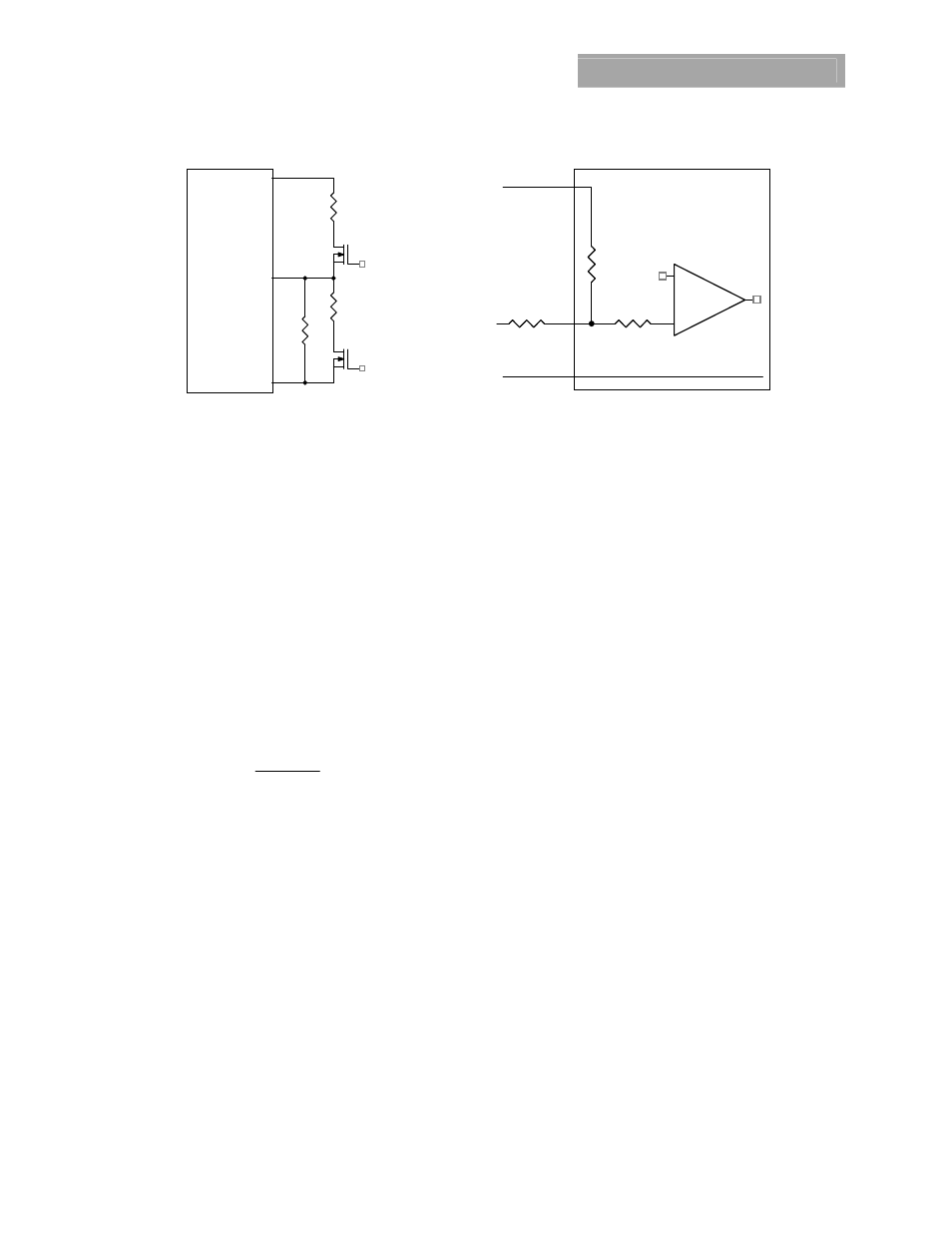

Figure 46. Circuit Configuration for margining Output

voltage

For proper voltage sequencing, first, input voltage is applied to

the module. The On/Off pin of the module is left unconnected

(or tied to GND for negative logic modules or tied to V

IN

for

positive logic modules) so that the module is ON by default.

After applying input voltage to the module, a minimum 10msec

delay is required before applying voltage on the SEQ pin.

During this time, a voltage of 50mV (± 20 mV) is maintained on

the SEQ pin.

This can be done by applying the sequencing voltage through

a resistor R1connected in series with the SEQ pin. This delay

gives the module enough time to complete its internal power-

up soft-start cycle. During the delay time, the SEQ pin should be

held close to ground (nominally 50mV ± 20 mV). This is required

to keep the internal op-amp out of saturation thus preventing

output overshoot during the start of the sequencing ramp. By

selecting resistor R1 (see fig. 47) according to the following

equation

05

.

0

24950

1

−

=

IN

V

R

ohms,

the voltage at the sequencing pin will be 50mV when the

sequencing signal is at zero.

After the 10msec delay, an analog voltage is applied to the SEQ

pin and the output voltage of the module will track this voltage

on a one-to-one volt bases until the output reaches the set-

point voltage. To initiate simultaneous shutdown of the

modules, the SEQ pin voltage is lowered in a controlled

manner. The output voltage of the modules tracks the voltages

below their set-point voltages on a one-to-one basis. A valid

input voltage must be maintained until the tracking and output

voltages reach ground potential.

Figure 47. Circuit showing connection of the sequencing

signal to the SEQ pin.

When using the EZ-SEQUENCE

TM

feature to control start-up of

the module, pre-bias immunity during start-up is disabled. The

pre-bias immunity feature of the module relies on the module

being in the diode-mode during start-up. When using the EZ-

SEQUENCE

TM

feature, modules goes through an internal set-up

time of 10msec, and will be in synchronous rectification mode

when the voltage at the SEQ pin is applied. This will result in

the module sinking current if a pre-bias voltage is present at

the output of the module. When pre-bias immunity during

start-up is required, the EZ-SEQUENCE

TM

feature must be

disabled. For additional guidelines on using the EZ-

SEQUENCE

TM

feature please refer to Application Note AN04-

008 “Application Guidelines for Non-Isolated Converters:

Guidelines for Sequencing of Multiple Modules”, or contact the

GE technical representative for additional information.

Power Good

The 12V MIcro TLynx

TM

12A

modules provide a Power Good

(PGOOD) signal that is implemented with an open-drain output

to indicate that the output voltage is within the regulation limits

of the power module. The PGOOD signal will be de-asserted to

a low state if any condition such as overtemperature,

overcurrent or loss of regulation occurs that would result in the

output voltage going ±11% outside the setpoint value. The

PGOOD terminal should be connected through a pullup resistor

(suggested value 100K

Ω) to a source of 6VDC or less.

Synchronization

The 12V Micro TLynx

TM

series of modules can be synchronized

using an external signal. Details of the SYNC signal are

provided in the Electrical Specifications table. If the

synchronization function is not being used, leave the SYNC pin

floating.

Tunable Loop

TM

The 12V Micro TLynx

TM

12A modules have a new feature that

optimizes transient response of the module called Tunable

Loop

TM

.

External capacitors are usually added to the output of the

module for two reasons: to reduce output ripple and noise (see

Figure 41) and to reduce output voltage deviations from the

Vo

MODULE

GND

Trim

Q1

Rtrim

Rmargin-up

Q2

Rmargin-down

R1

GND

VIN+

SEQ

+

-

OUT

10K

499K

MODULE