Pin description – Rainbow Electronics MAX3420E User Manual

Page 4

MAX3420E

USB Peripheral Controller

with SPI Interface

4

_______________________________________________________________________________________

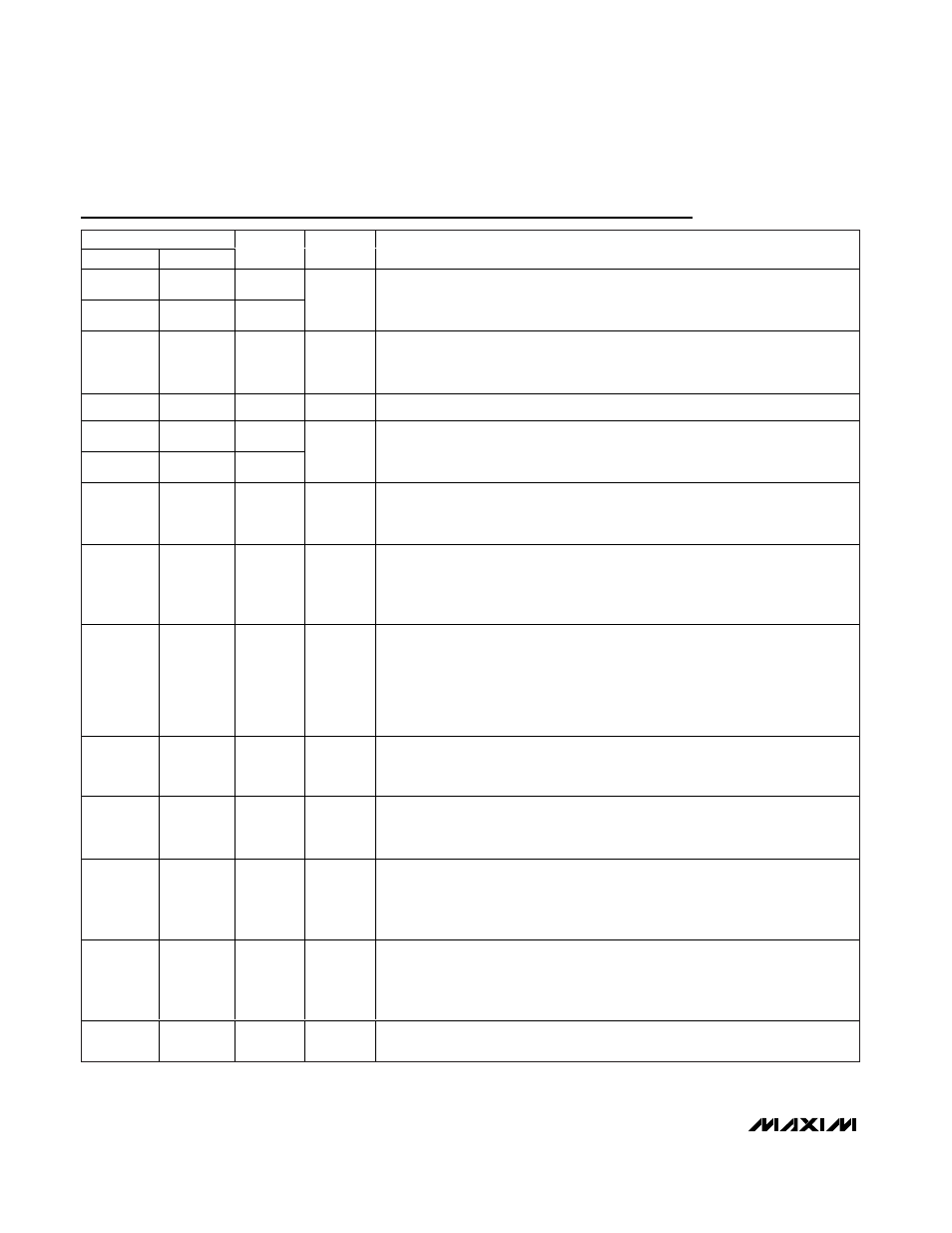

Pin Description

PIN

TQFN

TQFP

NAME

INPUT/

OUTPUT

FUNCTION

1

1

GPOUT0

2

2

GPOUT1

Output

G ener al - P ur p ose P ush- P ul l O utp uts. G P OU T3–G P OU T0 l og i c l evel s ar e r efer enced

to the vol tag e on V

L

. The S P I m aster contr ol s the G P OU T3–GP OU T0 states b y

w r i ti ng to b i t 3 thr oug h b i t 0 of the IOP IN S ( R20) r eg i ster .

3

3, 4

V

L

Input

Level-Translator Reference Voltage. Connect V

L

to the system’s 1.71V to 3.6V

logic-level power supply. Bypass V

L

to ground with a 0.1µF capacitor as close to

the V

L

pin as possible.

4, 14

5, 6, 18, 19

GND

Input

Ground

5

7

GPOUT2

6

8

GPOUT3

Output

Gener al - P ur p ose P ush- P ul l O utp uts. GP OU T3–GP O U T0 l og i c l evel s ar e r efer enced to

the vol tag e on V

L

. The S P I m aster contr ol s the GP O U T3–GP OU T0 states b y w r i ti ng to

b i t 3 thr oug h b i t 0 of the IOP IN S ( R20) r eg i ster .

7

10

RES

Input

Device Reset. Drive

RES low to clear all of the internal registers except for

PINCTL (R17), USBCTL (R15), and SPI logic

.

See the Device Reset section for a

description of resets available on the MAX3420E.

8

11

SCLK

Input

SPI Serial-Clock Input. An external SPI master supplies this clock with frequencies

up to 26MHz. The logic level is referenced to the voltage on V

L

. Data is clocked

into the SPI slave interface on the positive edge of SCLK. Data is clocked out of

the SPI slave interface on the falling edge of SCLK.

9

12

SS

Input

SPI Slave-Select Input. The

SS logic level is referenced to the voltage on V

L

.

When

SS is driven high, the SPI slave interface is not selected and SCLK

transitions are ignored. An SPI transfer begins with a high-to-low

SS transition and

ends with a low-to-high

SS transition. The MAX3420E SS pin is sensitive to

undershoot. A 33pF capacitor should be connected from

SS to ground to prevent

any noise spikes.*

10

13

MISO

Output

SPI Serial-Data Output (Master-In, Slave-Out). MISO is a push-pull output. MISO is

tri-stated in half-duplex mode or when

SS = 1. The MISO logic level is referenced

to the voltage on V

L

.

11

14

MOSI

Input or

Input/

Output

SPI Serial-Data Input (Master-Out, Slave-In). The logic level on MOSI is

referenced to the voltage on V

L

. MOSI can also be configured as a bidirectional

MOSI/MISO input and output.

12

15

GPX

Output

General-Purpose Multiplexed Output. The internal MAX3420E signal that appears

on GPX is programmable by writing to the GPXB and GPXA bits of the PINCTL

(R17) register. GPX indicates one of four signals: OPERATE (00, Default),

VBUS_DET (01), BUSACT (10), and SOF (11).

13

17

INT

Output

Inter r up t Outp ut. In ed g e m od e, the l og i c l evel on IN T i s r efer enced to the vol tag e

on V L. In ed g e m od e , IN T i s a p ush- p ul l outp ut w i th p r og r am m ab l e p ol ar i ty. In l evel

m od e, IN T i s op en d r ai n and acti ve l ow . S et the IE b i t i n the C P U C TL ( R16) r eg i ster to

enab l e

IN T.

15

20

D-

Input/

Output

U S B D - S i g nal . C onnect D - to a U S B “B” connector thr ough a 33

Ω ( ±1%) ser ies resi stor .

*33pF capacitor will not be required after redesign.