Typical operating characteristics, Detailed description – Rainbow Electronics MAX3420E User Manual

Page 12

MAX3420E

USB Peripheral Controller

with SPI Interface

12

______________________________________________________________________________________

Typical Operating Characteristics

(V

CC

= +3.3V, V

L

= +3.3V, T

A

= +25°C.)

Detailed Description

The MAX3420E contains the digital logic and analog

circuitry necessary to implement a full-speed USB

peripheral that complies with the USB specification rev

2.0. ESD protection of ±15kV is provided on D+, D-,

and VBCOMP. The MAX3420E features an internal USB

transceiver and an internal 1.5k

Ω resistor that connects

between D+ and V

CC

under the control of a register bit

(CONNECT). This allows a USB peripheral to control

the logical connection to the USB host. Any SPI master

can communicate with the MAX3420E through the SPI

slave interface that operates in SPI mode (0,0) or (1,1).

An SPI master accesses the MAX3420E by reading and

writing to internal registers. A typical data transfer con-

sists of writing a first byte that sets a register address

and direction with additional bytes reading or writing

data to the register or internal FIFO.

The MAX3420E contains 384 bytes of endpoint buffer

memory, implementing the following endpoints:

• EP0: 64-byte bidirectional CONTROL endpoint

• EP1: 2 x 64-byte double-buffered BULK/INT

OUT endpoint

• EP2: 2 x 64-byte double-buffered BULK/INT IN

endpoint

• EP3: 64-byte BULK/INT IN endpoint

The choice to use EP1–EP3 as BULK or INTERRUPT

endpoints is strictly a function of the endpoint descrip-

tors that the SPI master returns to the USB host during

enumeration.

The MAX3420E register set and SPI interface is optimized

to reduce SPI traffic. An interrupt output pin, INT, notifies

the SPI master when USB service is required: when a

packet arrives, a packet is sent, or the host suspends or

resumes bus activity. Double-buffered endpoints help

sustain bandwidth by allowing data to move concurrently

over USB and the SPI interface.

V

CC

Power the USB transceiver by applying a positive 3.3V

supply to V

CC

. Bypass V

CC

to GND with a 1.0µF

ceramic capacitor as close to the V

CC

pin as possible.

V

L

The MAX3420E digital core is powered though the V

L

pin. V

L

also acts as a reference level for the SPI inter-

face and all other inputs and outputs. Connect V

L

to the

system’s logic-level power supply. Internal level transla-

tors and V

L

allow the SPI interface and all general-pur-

pose inputs and outputs to operate at a system voltage

between 1.71V and 3.6V.

VBCOMP

The MAX3420E features a USB V

BUS

detector input,

VBCOMP. The VBCOMP pin can withstand input volt-

ages up to 6V. Bypass VBCOMP to GND with a 1.0µF

ceramic capacitor. According to USB specification rev

2.0, a self-powered USB device must not power the

1.5k

Ω pullup resistor on D+ if the USB host turns off

V

BUS

. VBCOMP is internally connected to a voltage

comparator so that the SPI master can detect the loss

of V

BUS

(through an interrupt (INT) or checking a bit

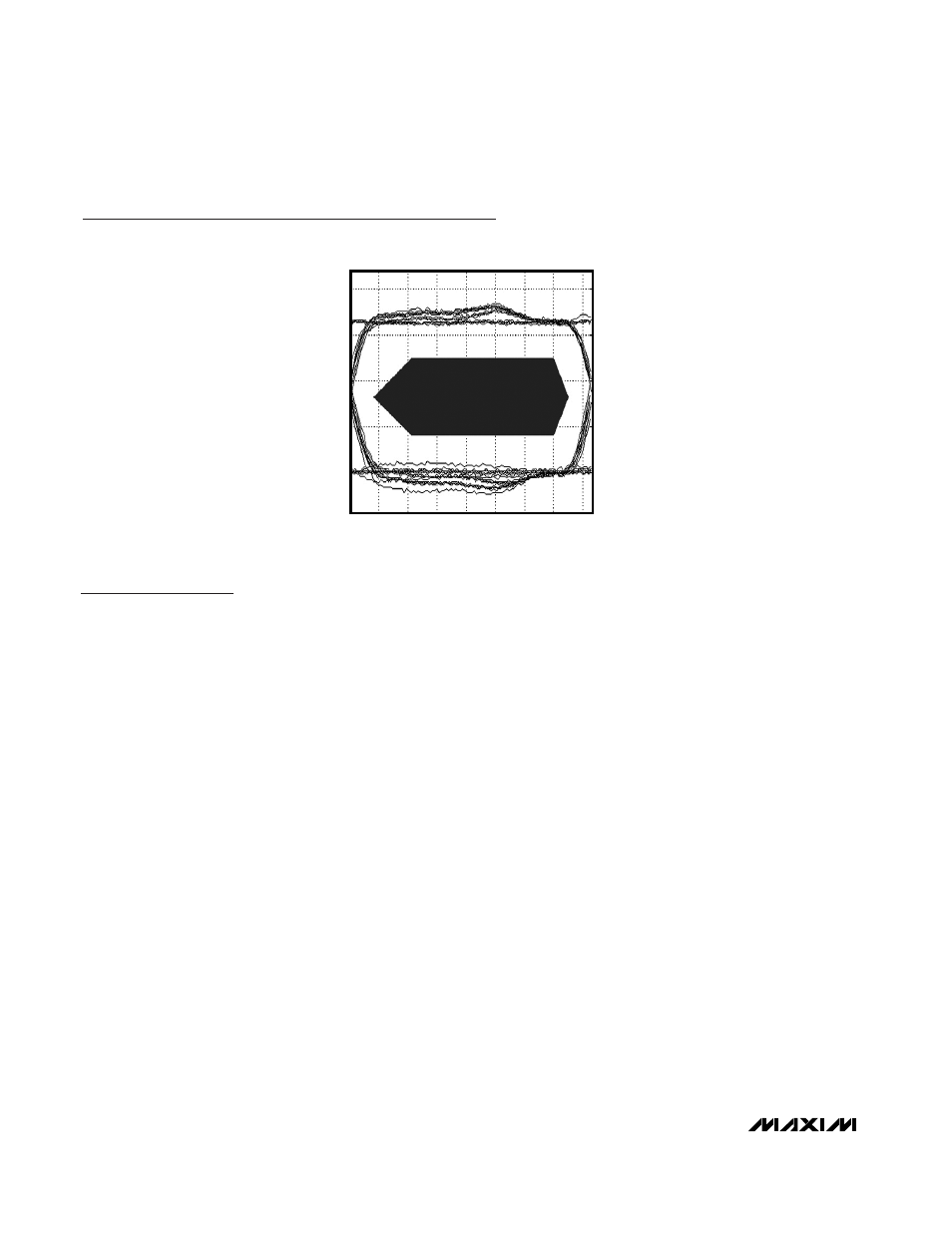

EYE DIAGRAM

MAX3420E toc01

4

1

0

-1

0

10

20

30

40

50

60

70

80

2

3

TIME (ns)

D+ AND D- (V)