Rainbow Electronics MAX3420E User Manual

Page 17

(5) To write SPI data, the SPI master keeps its output

driver on and clocks subsequent bytes into the

MOSI pin. To read SPI data, after the eighth clock

cycle the SPI master tri-states its output driver and

begins clocking in data bytes from the MOSI pin.

(6) The SPI master terminates the SPI cycle by return-

ing

SS high.

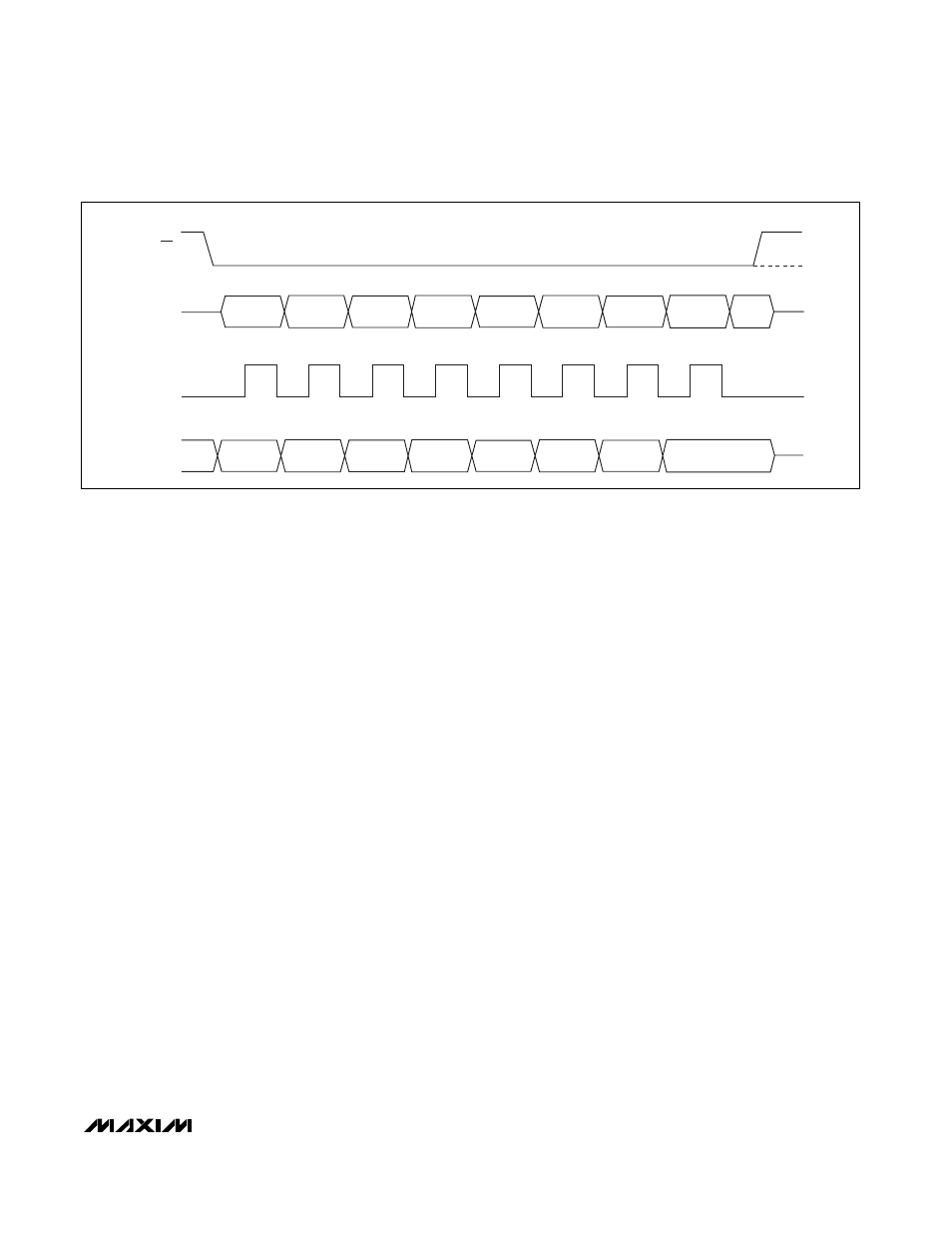

Figures 8 and 9 show timing diagrams for full- and half-

duplex operation.

USB Serial-Interface Engine

The serial-interface engine (SIE) does most of the

detailed work required by USB protocol:

• USB packet PID detection and checking

• CRC check and generation

• Automatic retries in case of errors

• USB packet generation

• NRZI data encoding and decoding

• Bit stuffing and unstuffing

• Various USB error condition detection

• USB bus reset, suspend, and wake-up detection

• USB resume signaling

• Automatic flow control (NAK)

PLL

An internal PLL multiplies the 12MHz oscillator signal

by four to produce an internal 48MHz clock. When the

chip is powered-down, the oscillator is turned off to

conserve power. When re-powered, the oscillator and

PLL require time to stabilize and lock. The OSCOKIRQ

interrupt bit is used to indicate to the SPI master that

the clocking system is stable and ready for operation.

Power Management

According to USB rev. 2.0 specification, when a USB

host stops sending traffic for at least 3 milliseconds to a

peripheral, the peripheral must enter a power-down

state called SUSPEND. Once suspended, the peripher-

al must have enough of its internal logic active to rec-

ognize when the host resumes signaling, or if enabled

for remote wakeup, that the SPI master wishes to signal

a resume event. The following sections titled Suspend

and Wakeup and USB Resume describe how the SPI

master coordinates with the MAX3420E to accomplish

this power management.

Suspend

After three milliseconds of USB bus inactivity, a USB

peripheral is required to enter the USB suspend state

and draw no more than 500µA of supply current. To

accomplish this, after three milliseconds of USB bus

inactivity, the MAX3420E sets the SUSPIRQ bit in the

USBIRQ (R13) register and asserts the INT output, if

SUSPIE = 1 and IE = 1. The SPI master must do any

necessary power-saving housekeeping and then set

the PWRDOWN bit in the USBCTL (R15) register. This

instructs the MAX3420E to enter a power-down state, in

which it does the following:

• Stops the 12MHz oscillator

• Keeps the INT output active (according to the

mode set in the PINCTL (R17) register)

• Monitors the USB D+ line for bus activity

• Monitors the SPI port for any traffic

Note that the MAX3420E does not automatically enter

a power-down state after three milliseconds of bus

inactivity. This allows the SPI master to perform any

MAX3420E

USB Peripheral Controller

with SPI Interface

______________________________________________________________________________________

17

SS

MISO

MOSI

SCLK

SPI MODE 0,0 (CPOL = 0, CPHA = 0)

SUSPIRQ

URESIRQ

SUDAVIRQ

IN3BAVIRQ

IN2BAVIRQ

REG 4

REG 3

REG 2

REG 1

REG 0

0

DIR

ACKSTAT

OUT1DAVIRQ OUT0DAVIRQ

IN0BAVIRQ

X

Figure 15. SPI Port in Full-Duplex Mode