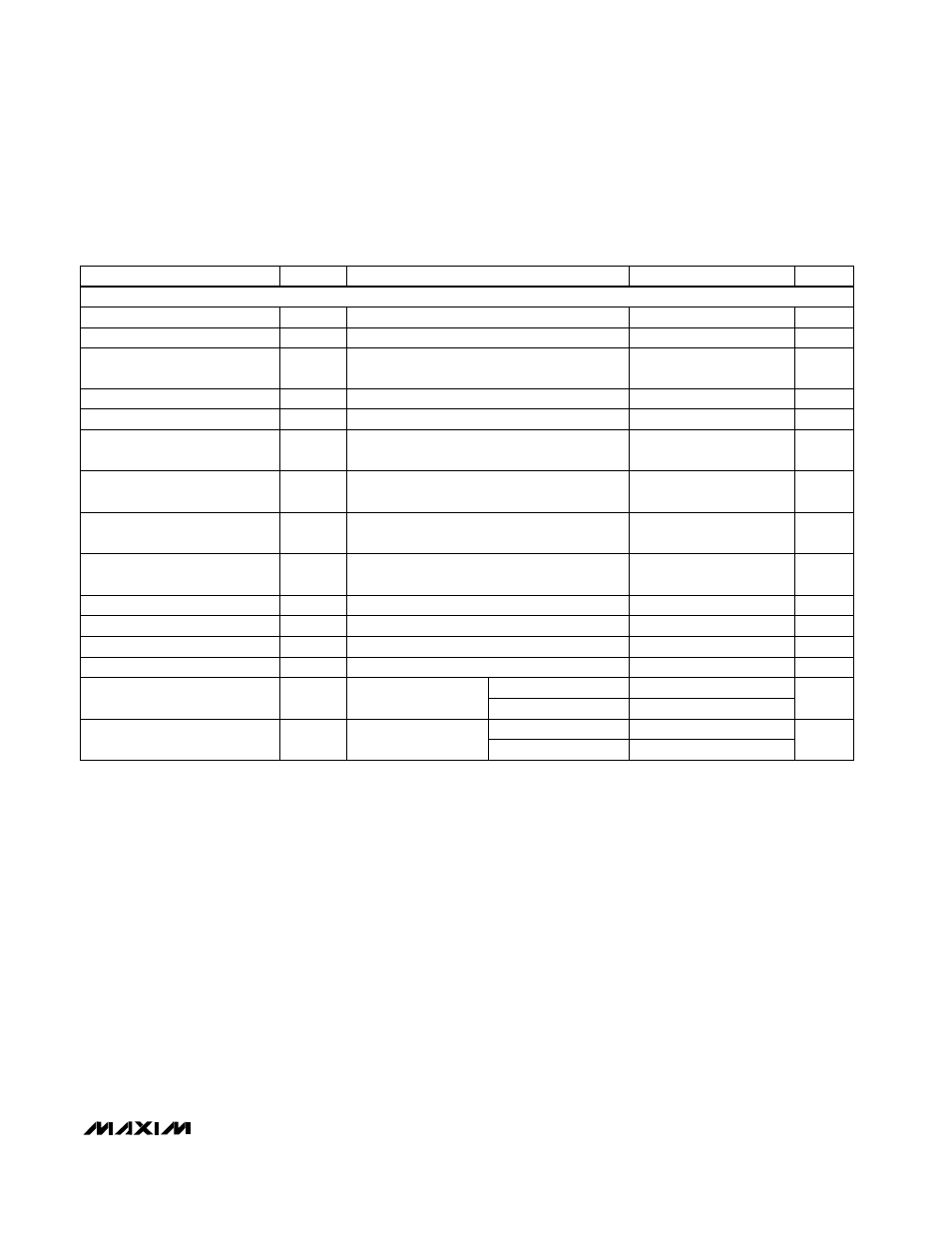

Ac electrical characteristics (continued) – Rainbow Electronics MAX106 User Manual

Page 5

MAX106

±5V, 600Msps, 8-Bit ADC with On-Chip

2.2GHz Bandwidth Track/Hold Amplifier

_______________________________________________________________________________________

5

CONDITIONS

UNITS

MIN

TYP

MAX

SYMBOL

PARAMETER

20% to 80%, C

L

= 3pF

20% to 80%, C

L

= 3pF

20% to 80%, C

L

= 3pF

Figure 17

Figure 17

Figure 15

Figure 15

Figure 4

Figure 17

ps

220

t

RDREADY

DREADY Rise Time

ps

360

t

FDATA

DATA Fall Time

ps

420

t

RDATA

DATA Rise Time

ps

-50

150

350

t

PD2

DREADY to DATA Propagation

Delay (Note 14)

ns

2.2

t

PD1

CLK to DREADY Propagation

Delay

ps

0

t

HD

Reset Input Data Hold Time

(Note 13)

ps

0

t

SU

Reset Input Data Setup Time

(Note 13)

ps

< 0.5

t

AJ

Aperture Jitter

ps

100

t

AD

Aperture Delay

DIV1, DIV2 modes

DIV1, DIV2 modes

20% to 80%, C

L

= 3pF

9.5

Clock

Cycles

8.5

t

PDA

Auxiliary Port Pipeline Delay

Clock

Cycles

7.5

t

PDP

Primary Port Pipeline Delay

ps

180

t

FDREADY

DREADY Fall Time

AC ELECTRICAL CHARACTERISTICS (continued)

(V

CC

A = V

CC

I = V

CC

D = +5.0V, V

EE

= -5.0V, V

CC

O = +3.3V, REFIN connected to REFOUT, f

S

= 600Msps, f

IN

at -1dBFS, T

A

= +25°C,

unless otherwise noted.)

Note 1: Static linearity parameters are computed from a “best-fit” straight line through the code transition points. The full-scale

range (FSR) is defined as 256

·

slope of the line.

Note 2: The offset control input is a self-biased voltage divider from the internal +2.5V reference voltage. The nominal open-circuit

voltage is +1.25V. It may be driven from an external potentiometer connected between REFOUT and GNDI.

Note 3: The clock input’s termination voltage can be operated between -2.0V and GNDI. Observe the absolute maximum ratings on

the CLK+ and CLK- inputs.

Note 4: Input logic levels are measured with respect to the V

CC

O power-supply voltage.

Note 5: All PECL digital outputs are loaded with 50

Ω to V

CC

O - 2.0V. Measurements are made with respect to the V

CC

O power-

supply voltage.

Note 6: The current in the V

CC

O power supply does not include the current in the digital output’s emitter followers, which is a func-

tion of the load resistance and the V

TT

termination voltage.

Note 7: Common-mode rejection ratio is defined as the ratio of the change in the transfer-curve offset voltage to the change in the

common-mode voltage, expressed in dB.

Note 8: Measured with the positive supplies tied to the same potential, V

CC

A = V

CC

D = V

CC

I. V

CC

varies from +4.75V to +5.25V.

Note 9: V

EE

varies from -5.25V to -4.75V.

Note 10: Power-supply rejection ratio is defined as the ratio of the change in the transfer-curve offset voltage to the change in power

supply voltage, expressed in dB.

Note 11: Effective number of bits (ENOB) are computed from a curve fit referenced to the theoretical full-scale range.

7.5

Msps

600

f

MAX

Maximum Sample Rate

Figure 17

ns

0.75

t

PWL

Clock Pulse Width Low

Figure 17

ns

0.75

5

t

PWH

Clock Pulse Width High

TIMING CHARACTERISTICS

Figures 6, 7, and 8

Figures 6, 7, and 8

DIV4 mode

DIV4 mode