Table 3. spi data format (continued) – Rainbow Electronics MAX2063 User Manual

Page 18

MAX2063

Dual 50MHz to 1000MHz High-Linearity,

Serial/Parallel-Controlled Digital VGA

18

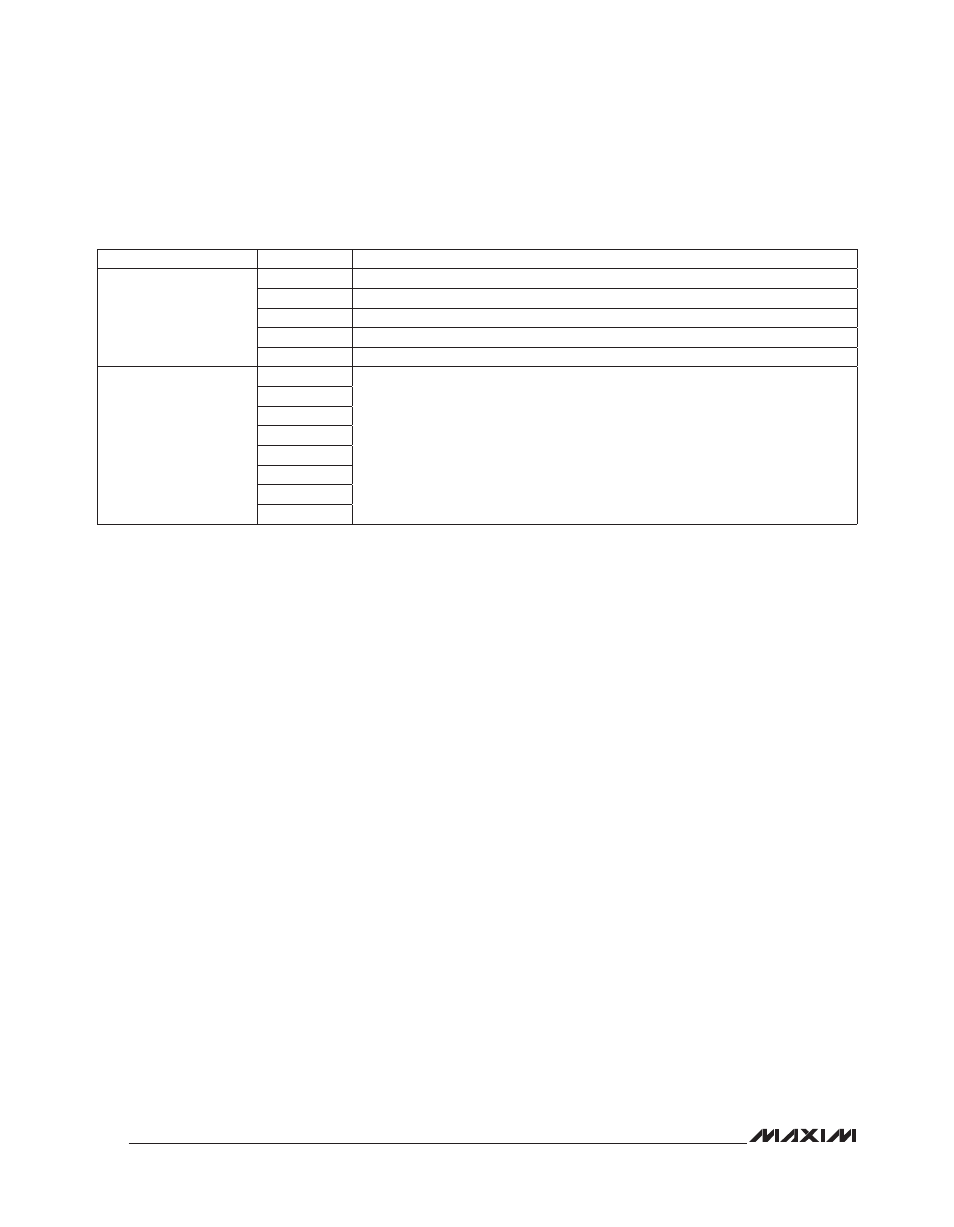

Table 3. SPI Data Format (continued)

Digital Attenuator Settings Using

the Parallel Control Bus

To capitalize on its fast 25ns switching capability, the

device offers a supplemental 5-bit parallel control inter-

face for each attenuator. The two buses of the digital

logic attenuator-control pins (D0_ _–D4_ _) enable the

attenuator stages (Table 4).

Direct access to these 5-bit buses enables the user to

avoid any programming delays associated with the SPI

interface. One of the limitations of any SPI bus is the

speed at which commands can be clocked into each

peripheral device. By offering direct access to the 5-bit

parallel interface, the user can quickly shift between

digital attenuator states as needed for critical “fast-

attack” automatic gain-control (AGC) applications.

Note that when the digital attenuators are controlled

by the SPI bus, the control voltages of each digital

attenuator show on the five parallel control pins (pins

14–17, 19 for digital attenuator 2, and pins 42, 44–47 for

digital attenuator 1). When the digital attenuators are in

SPI mode, the parallel control pins must be open.

“Rapid-Fire” Preprogrammed

Attenuation States

The device has an added feature that provides

“rapid-fire” gain selection between four preprogrammed

attenuation steps. As with the supplemental 5-bit buses

previously mentioned, this “rapid-fire” gain selection

allows the user to quickly access any one of four

customized digital attenuation states without incurring

the delays associated with reprogramming the device

through the SPI bus.

The switching speed is comparable to that achieved

using the supplemental 5-bit parallel buses. However,

by employing this specific feature, the digital attenuator

I/O is further reduced by a factor of either 5 or 2.5 (5

control bits vs. 1 or 2, respectively), depending on the

number of states desired.

The user can employ the STA_A_1 and STA_B_1

(STA_A_2 and STA_B_2 for attenuator 2) logic input pins

to apply each step as required (see Tables 5 and 6).

Toggling just the STA_A_1 pin (1 control bit) yields two

preprogrammed attenuation states; toggling both the

STA_A_1 and STA_B_1 pins together (2 control bits)

yields four preprogrammed attenuation states.

As an example, assume that the AGC application

requires a static attenuation adjustment to trim out

gain inconsistencies within a receiver lineup. The same

AGC circuit can also be called upon to dynamically

attenuate an unwanted blocker signal that could desense

the receiver and lead to an ADC overdrive condition. In

this example, the device would be preprogrammed

(through the SPI bus) with two customized attenuation

states—one to address the static gain-trim adjustment,

the second to counter the unwanted blocker condition.

Toggling just the STA_A_1 control bit enables the

user to switch quickly between the static and dynamic

attenuation settings with only one I/O pin.

FUNCTION

BIT

DESCRIPTION

1st Digital Attenuator

State 1

D12

16dB step (MSB of the 5-bit word used to program the digital attenuator state 1)

D11

8dB step

D10

4dB step

D9

2dB step

D8

1dB step

Reserved

D7

Bits D[7:0] are reserved. Set to logic 0.

D6

D5

D4

D3

D2

D1

D0 (LSB)