Rainbow Electronics MAX2063 User Manual

Page 16

MAX2063

Dual 50MHz to 1000MHz High-Linearity,

Serial/Parallel-Controlled Digital VGA

16

1st Digital Attenuator Programming

D0:D7

Reserved. Set to logic 0.

D8:D12

Preprogrammed Attenuation State 1

D8 = 1dB bit, D9 = 2dB bit, D10 = 4dB bit,

D11 = 8dB bit, D12 = 16dB bit

D13:D17 Preprogrammed Attenuation State 2

D13 = 1dB bit, D14 = 2dB bit, D15 = 4dB bit,

D16 = 8dB bit, D17 = 16dB bit

D18:D22 Preprogrammed Attenuation State 3

D18 = 1dB bit, D19 = 2dB bit, D20 = 4dB bit,

D21 = 8dB bit, D22 = 16dB bit

D23:D27 Preprogrammed Attenuation State 4

D23 = 1dB bit, D24 = 2dB bit, D25 = 4dB bit,

D26 = 8dB bit, D27 = 16dB bit

2nd Digital Attenuator Programming

D28:D35 Reserved. Set to logic 0.

D36:D40 Preprogrammed Attenuation State 1

D36 = 1dB bit, D37 = 2dB bit, D38 = 4dB bit,

D39 = 8dB bit, D40 = 16dB bit

D41:D45 Preprogrammed Attenuation State 2

D41 = 1dB bit, D42 = 2dB bit, D43 = 4dB bit,

D44 = 8dB bit, D45 = 16dB bit

D46:D50 Preprogrammed Attenuation State 3

D46 = 1dB bit, D47 = 2dB bit, D48 = 4dB bit,

D49 = 8dB bit, D50 = 16dB bit

D51:D55 Preprogrammed Attenuation State 4

D51 = 1dB bit, D52 = 2dB bit, D53 = 4dB bit,

D54 = 8dB bit, D55 = 16dB bit

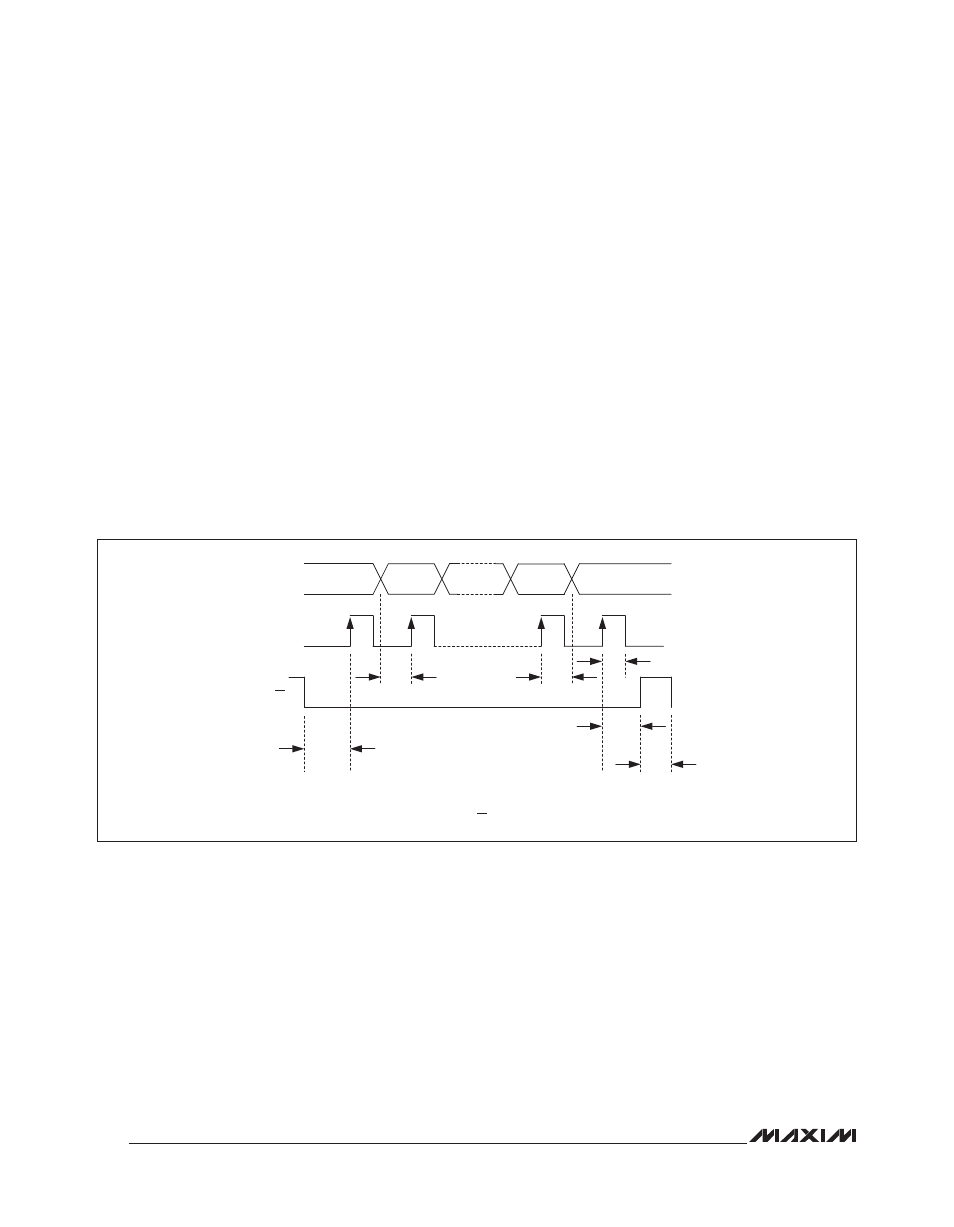

Figure 1. SPI Timing Diagram

t

CS

MSB

LSB

DN

D1

D0

D(N-1)

t

CH

t

CW

t

ES

t

EW

t

EWS

DATA

CLOCK

CS

DATA ENTERED ON CLOCK RISING EDGE.

ATTENUATOR REGISTER STATE CHANGE ON CS RISING EDGE.

N = NUMBER OF DATA BITS.

NOTES: