Applications information – Rainbow Electronics MAX510 User Manual

Page 14

MAX509/MAX510

Quad, Serial 8-Bit DACs

with Rail-to-Rail Outputs

14

______________________________________________________________________________________

If multiple devices share a common DIN line, Figure 7's

configuration provides simultaneous update by strob-

ing

LDAC low. CS1, CS2, CS3... are driven separately,

thus controlling which data are written to devices 1, 2, 3....

Analog Section

DAC Operation

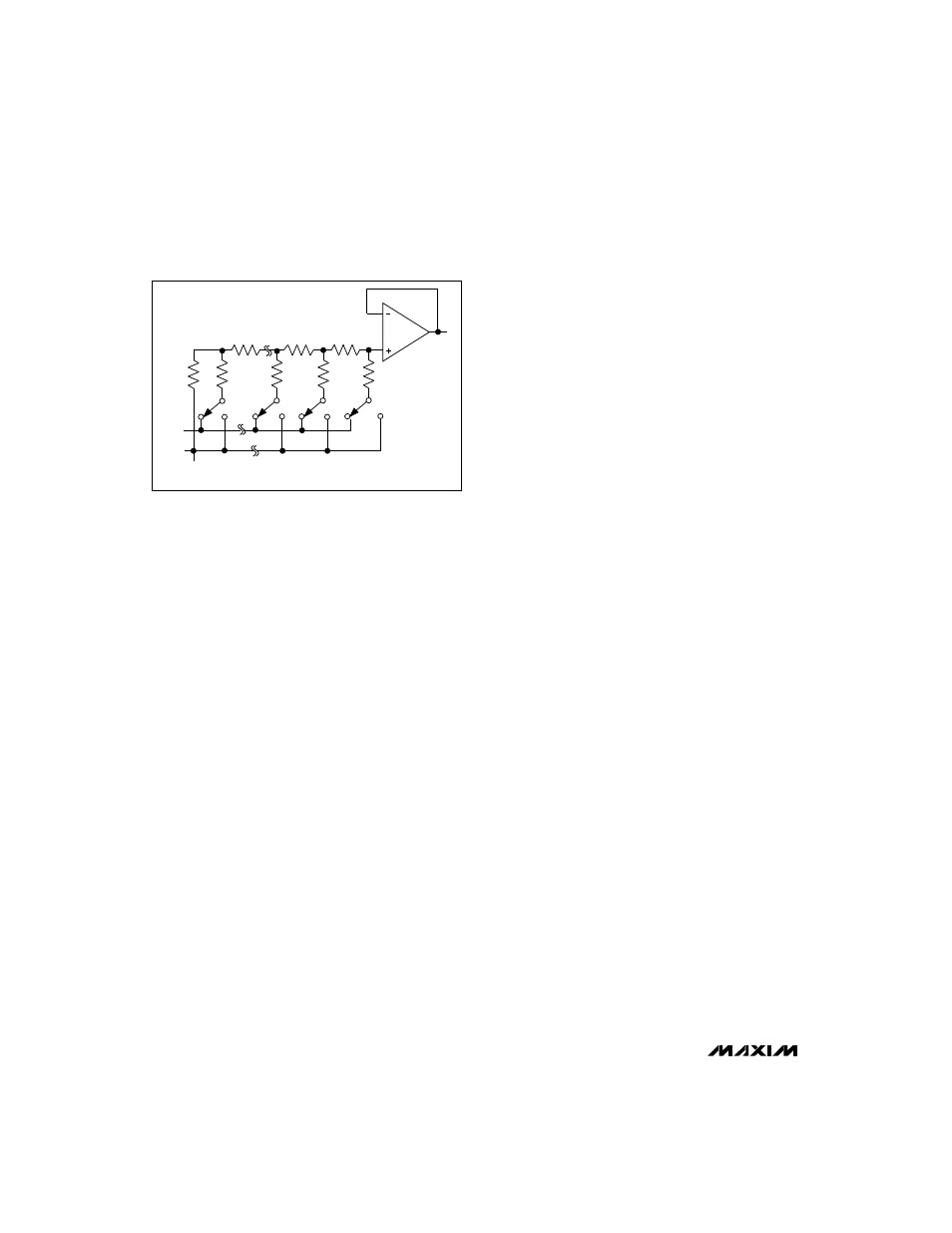

The MAX509/MAX510 contain four matched voltage-

output DACs. The DACs are inverted R-2R ladder net-

works that convert 8-bit digital words into equivalent

analog output voltages in proportion to the applied ref-

erence voltages. Each DAC in the MAX509 has a sepa-

rate reference input, while the two reference inputs in

the MAX510 each share a pair of DACs. The two refer-

ence inputs permit different full-scale output voltage

ranges for each pair of DACs. A simplified diagram of

one of the four DACs is shown in Figure 8.

Reference Input

The MAX509/MAX510 can be used for multiplying

applications. The reference accepts both DC and AC

signals. The voltage at each REF input sets the full-

scale output voltage for its respective DAC(s). If the ref-

erence voltage is positive, both the MAX509 and

MAX510 can be operated from a single supply. If dual

supplies are used, the reference input can vary from

V

SS

to V

DD

, but is always referred to AGND. The input

impedance at REF is code dependent, with the lowest

value (16k

Ω

for the MAX509 and 8k

Ω

for the MAX510)

occurring when the input code is 55 hex or 0101 0101.

The maximum value, practically infinity, occurs when

the input code is 00 hex. Since the REF input imped-

ance is code dependent, the DAC's reference sources

must have a low output impedance (no more than 32

Ω

for the MAX509 and 16

Ω

for the MAX510) to maintain

output linearity. The REF input capacitance is also code

dependent: 15pF typical for the MAX509 and 30pF

typical for the MAX510.

The output voltage for any DAC can be represented by

a digitally programmable voltage source as:

VOUT = (NB x VREF) / 256

where NB is the numerical value of the DAC's binary

input code.

Output Buffer Amplifiers

All MAX509/MAX510 voltage outputs are internally

buffered by precision unity-gain followers that slew at

up to 1V/µs. The outputs can swing from V

SS

to V

DD

.

With a 0V to +4V (or +4V to 0V) output transition, the

amplifier outputs will settle to 1/2LSB in typically 6µs

when loaded with 10k

Ω

in parallel with 100pF.

The buffer amplifiers are stable with any combination of

resistive loads

≥

2k

Ω

and capacitive loads

≤

300pF.

__________Applications Information

Power Supply and

Reference Operating Ranges

The MAX509/MAX510 are fully specified to operate with

V

DD

= 5V ±10% and V

SS

= 0V to -5.5V. 8-bit perfor-

mance is guaranteed for both single- and dual-supply

operation. The zero-code output error is less than 14mV

when operating from a single +5V supply.

The DACs work well with reference voltages from V

SS

to V

DD

. The reference voltage is referred to AGND.

The preferred power-up sequence is to apply V

SS

and

then V

DD

, but bringing up both supplies at the same

time is also acceptable. In either case, the voltage

applied to REF should not exceed V

DD

during power-

up or at any other time. If proper power sequencing is

not possible, connect an external Schottky diode

between V

SS

and AGND to ensure compliance with the

Absolute Maximum Ratings. Do not apply signals to

the digital inputs before the device is fully powered up.

Power-Supply Bypassing

and Ground Management

In single-supply operation (AGND = DGND = V

SS

=

0V), AGND, DGND and V

SS

should be connected

together in a "star" ground at the chip. This ground

should then return to the highest quality ground avail-

able. Bypass V

DD

with a 0.1µF capacitor, located as

close to V

DD

and DGND as possible. In dual-supply

operation, bypass V

SS

to AGND with 0.1µF.

Careful PC board layout minimizes crosstalk among

DAC outputs, reference inputs, and digital inputs.

Figures 9 and 10 show suggested circuit board layouts

to minimize crosstalk.

2R

R

R

R

2R

2R

2R

2R

2R

D0

D5

D6

D7

REF_

AGND

SHOWN FOR ALL 1 ON DAC

OUT_

Figure 8. DAC Simplified Circuit Diagram