Rainbow Electronics BR24L32FV-W User Manual

Page 4

BR24L32-W / BR24L32F-W / BR24L32FJ-W / BR24L32FV-W

Memory ICs

4/25

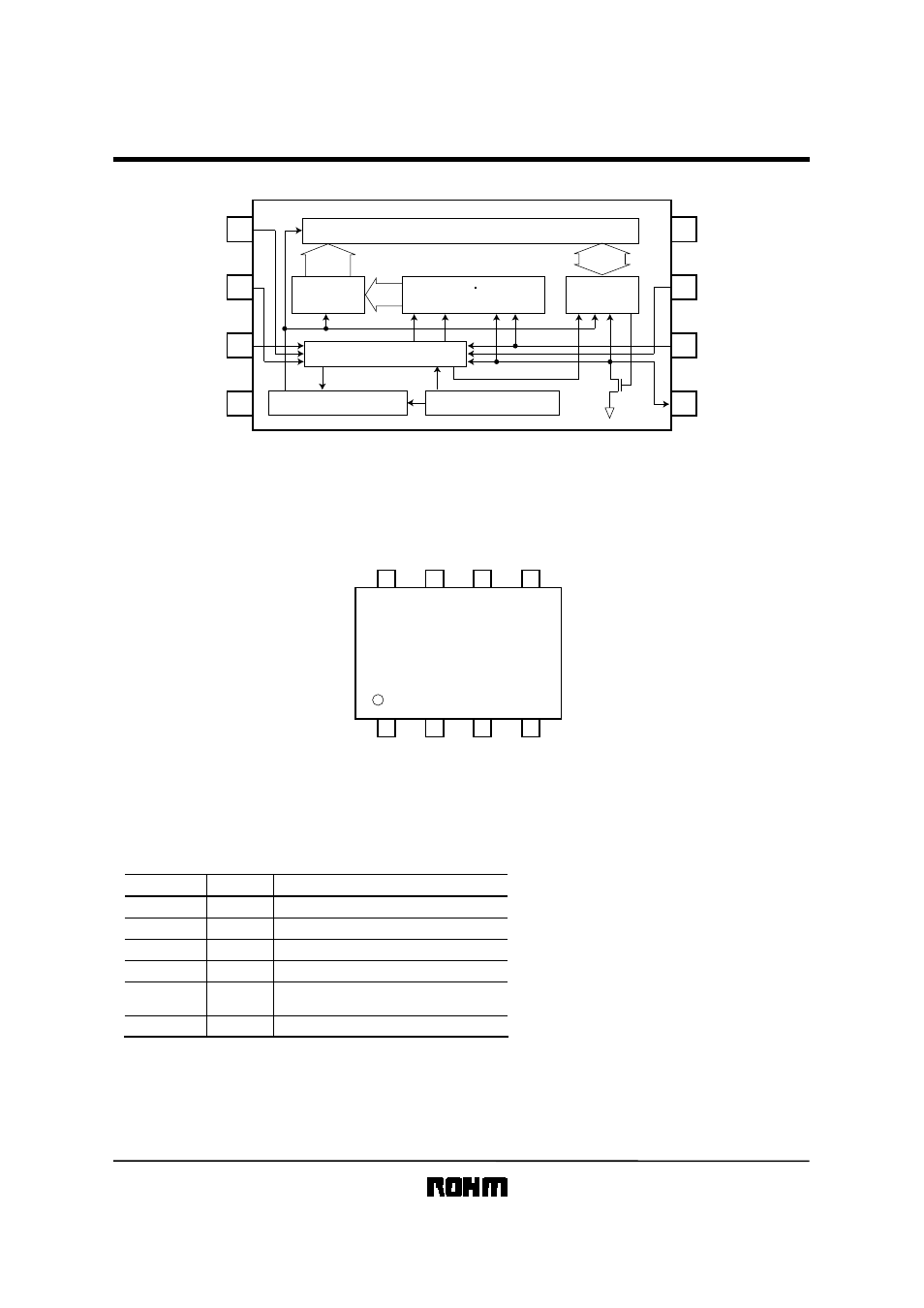

zBlock diagram

1

A0

A1

2

A2

3

GND

4

V

CC

8

WP

7

6

SCL

SDA

5

32kbit EEPROM array

Control logic

High voltage generator

Vcc level detect

12bit

8bit

ACK

STOP

START

Address

decoder

Slave word

address register

12bits

Data

register

Fig.2 BLOCK DIAGRAM

zPin configuration

BR24L32-W

BR24L32F-W

BR24L32FJ-W

BR24L32FV-W

V

CC

A0

WP

A1

SCL

A2

SDA

GND

1

2

3

4

5

6

7

8

Fig.3 PIN LAYOUT

zPin name

Write protect input

Power supply

Function

Ground (0V)

Slave address set

Serial clock input

SDA

V

CC

A0, A1, A2

Pin name

GND

WP

SCL

I / O

−

−

IN

IN

IN

IN / OUT

Slave and word address,

serial data input, serial data output

∗

An open drain output requires a pull-up resistor.

∗

See also other documents in the category Rainbow Electronics Storage:

- W27E010 (14 pages)

- W27L520 (16 pages)

- W29EE512 (21 pages)

- W27E512 (16 pages)

- W24100 (11 pages)

- W27E040 (15 pages)

- W25Q32 (60 pages)

- W49L102 (21 pages)

- W29C040 (20 pages)

- W29EE011 (20 pages)

- W49F020 (21 pages)

- W2465 (10 pages)

- W24256 (10 pages)

- W982516CH (43 pages)

- MAX16014 (12 pages)

- W24512A (10 pages)

- W27E020 (14 pages)

- W29C020C (21 pages)

- W25X64 (47 pages)

- W24257 (11 pages)

- W24L257 (10 pages)

- W9864G2GH (48 pages)

- W24L11 (11 pages)

- W27L010 (14 pages)

- W27E520 (16 pages)

- W27LE520 (16 pages)

- W9825G6CH (43 pages)

- W49F002U (23 pages)

- W9864G6GB (47 pages)

- AT45DB011B (32 pages)

- AT45DB642 (71 pages)

- AT45DB642 (37 pages)

- AT45DB161D (51 pages)

- AT27LV040A (12 pages)

- AT29LV010A (15 pages)

- HT24LC08 (11 pages)

- AT29C257 (12 pages)

- AT45DB161B (32 pages)

- AT27C1024 (12 pages)

- AT28BV256 (12 pages)

- AT28C040 (12 pages)

- DS1258Y_AB (9 pages)

- AT28BV64B (12 pages)

- AT27C512R (12 pages)

- DS1220AB_AD (9 pages)