6 write configuration register, 1 quad enable command – Rainbow Electronics AT45DQ161 User Manual

Page 36

36

AT45DQ161 [ADVANCE DATASHEET]

8790A–DFLASH–11/2012

9.6

Write Configuration Register

The Write Configuration Register commands are used to modify the QE bit of the non-volatile Configuration Register.

There are two commands that are utilized to enable and disable the Quad I/O functionality of the device and they are the

Quad Enable and Quad Disable commands, respectively.

The Configuration Register is a non-volatile register and is subject to the same program/erase endurance characteristics

of the Main Memory Array. The programming of the Configuration Register is internally self-timed and should take place

in a time of t

WRCR.

While the Configuration Register is being updated, the Status Register can be read and will indicate

that the device is busy. For faster throughput, it is recommended that the Status Register be polled rather than waiting

the t

WRCR

time to determine if the Configuration Register has completed the programming cycle.

9.6.1

Quad Enable Command

The Quad Enable command is used to program the QE bit of the non-volatile Configuration Register to a Logical 1 to

enable the Quad I/O functionality of the device. To issue the Quad Enable command, the CS pin must first be asserted

followed by a four byte opcode of 3Dh, 2Ah, 81h, and 66h.

After the last bit of the four byte opcode has been clocked in, the CS pin must be deasserted allowing the QE bit of the

Configuration Register to be modified within the time of t

WRCR

.

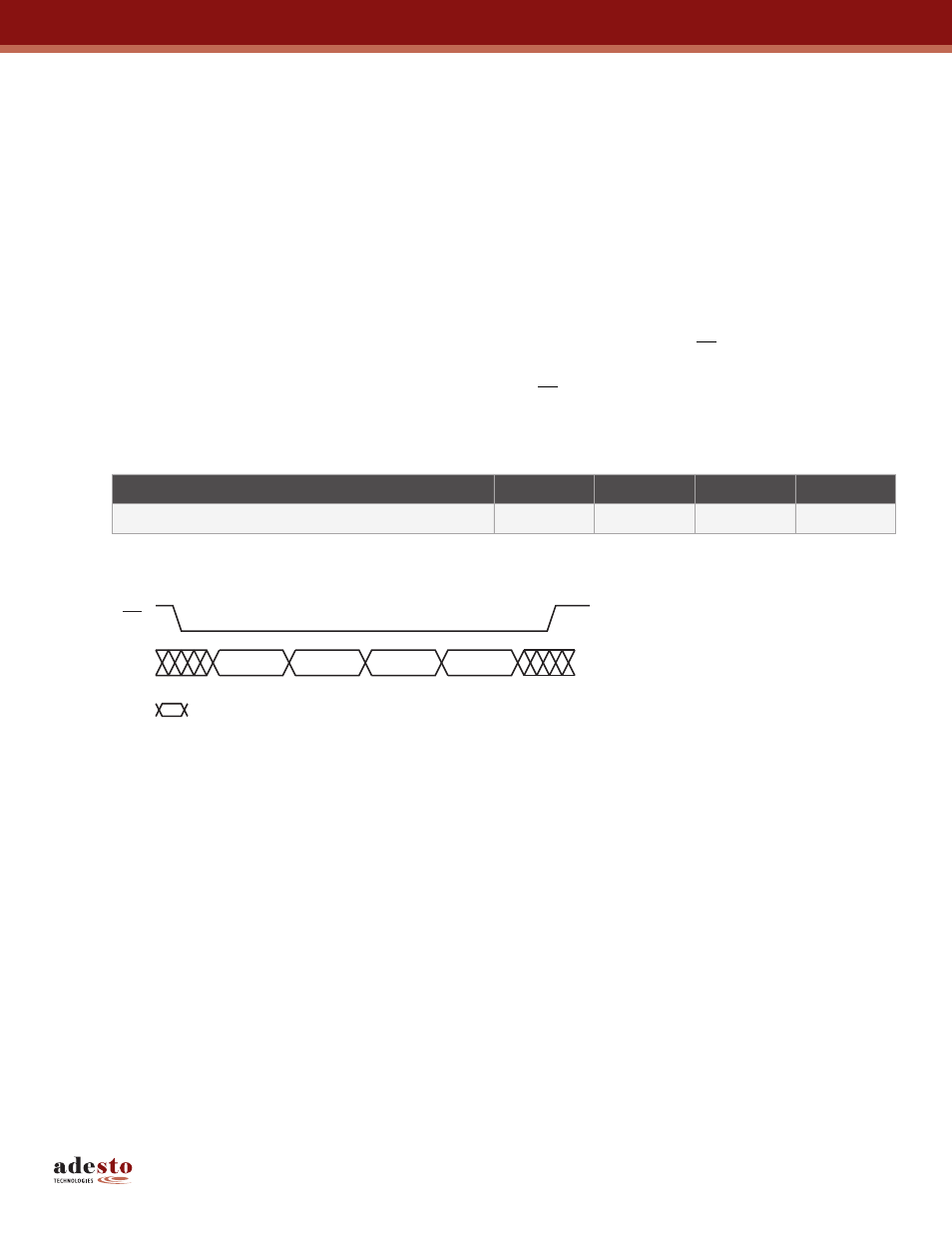

Table 9-3.

Quad Enable Command

Figure 9-3. Quad Enable

Command

Byte 1

Byte 2

Byte 3

Byte 4

Quad Enable

3Dh

2Ah

81h

66h

3Dh

2Ah

81h

66h

CS

SI

Each transition represents eight bits