Mcu control register – mcucr, Attiny11/12 – Rainbow Electronics ATtiny12 User Manual

Page 28

28

ATtiny11/12

1006C–09/01

MCU Control Register –

MCUCR

The MCU Control Register contains control bits for general MCU functions.

Note:

The Pull-up Disable (PUD) bit is only available in ATtiny12.

• Bit 7 - Res: Reserved Bit

This bit is a reserved bit in the ATtiny11/12 and always reads as zero.

• Bit 6 - Res: Reserved Bit in ATtiny11

This bit is a reserved bit in the ATtiny11 and always reads as zero.

• Bit 6 - PUD: Pull-up Disable in ATtiny12

Setting this bit, disables all pull-ups on port B. If this bit is cleared, the pull-ups can be

individually enabled as described in section “I/O Port B” on page 41.

• Bit 5 - SE: Sleep Enable

The SE bit must be set (one) to make the MCU enter the Sleep Mode when the SLEEP

instruction is executed. To avoid the MCU entering the Sleep Mode unless it is the pro-

grammer’s purpose, it is recommended to set the Sleep Enable SE bit just before the

execution of the SLEEP instruction.

• Bit 4 - SM: Sleep Mode

This bit selects between the two available sleep modes. When SM is cleared (zero), Idle

Mode is selected as Sleep Mode. When SM is set (one), Power-down Mode is selected

as Sleep Mode. For details, refer to the paragraph “Sleep Modes” below.

• Bits 3, 2 - Res: Reserved Bits

These bits are reserved bits in the ATtiny11/12 and always read as zero.

• Bits 1, 0 - ISC01, ISC00: Interrupt Sense Control0 Bit 1 and Bit 0

The External Interrupt 0 is activated by the external pin INT0 if the SREG I-flag and the

corresponding interrupt mask are set. The following table shows how to set the ISC bits

to generate an external interrupt:

The value on the INT0 pin is sampled before detecting edges. If edge interrupt is

selected, pulses that last longer than one CPU clock period will generate an interrupt.

Shorter pulses are not guaranteed to generate an interrupt. If low-level interrupt is

selected, the low level must be held until the completion of the currently executing

instruction to generate an interrupt. If enabled, a level-triggered interrupt will generate

an interrupt request as long as the pin is held low.

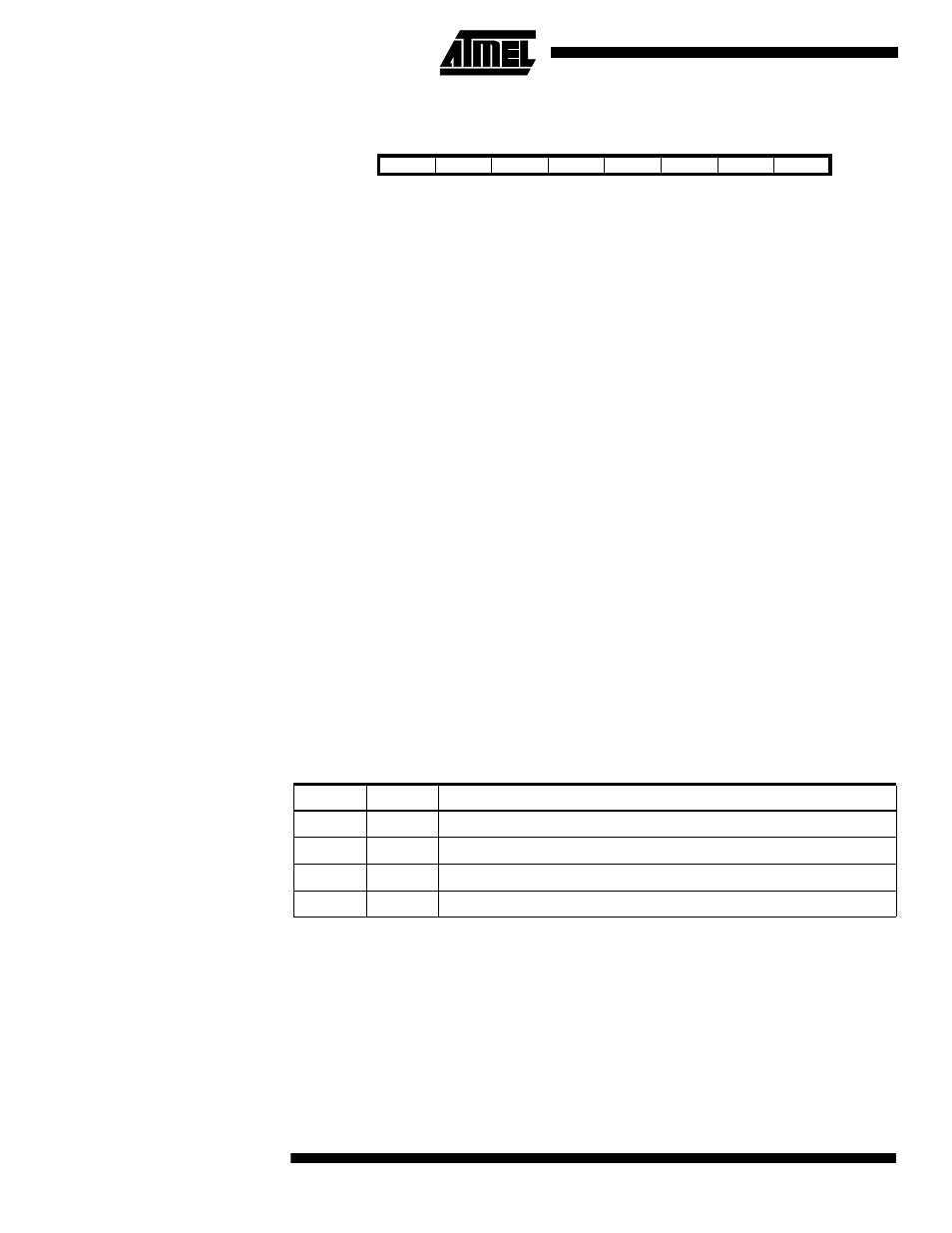

Bit

7

6

5

4

3

2

1

0

$35

-

(PUD)

SE

SM

-

-

ISC01

ISC00

MCUCR

Read/Write

R

R(/W)

R/W

R/W

R

R

R/W

R/W

Initial Value

0

0

0

0

0

0

0

0

Table 13. Interrupt 0 Sense Control

ISC01

ISC00

Description

0

0

The low level of INT0 generates an interrupt request.

0

1

Any change on INT0 generates an interrupt request

1

0

The falling edge of INT0 generates an interrupt request.

1

1

The rising edge of INT0 generates an interrupt request.