Table 16. mfr_mode bit definition – Rainbow Electronics MAX16064 User Manual

Page 44

MAX16064

±0.3% Accurate, Quad, Power-Supply Controller with

Active-Voltage Output Control and PMBus Interface

44

______________________________________________________________________________________

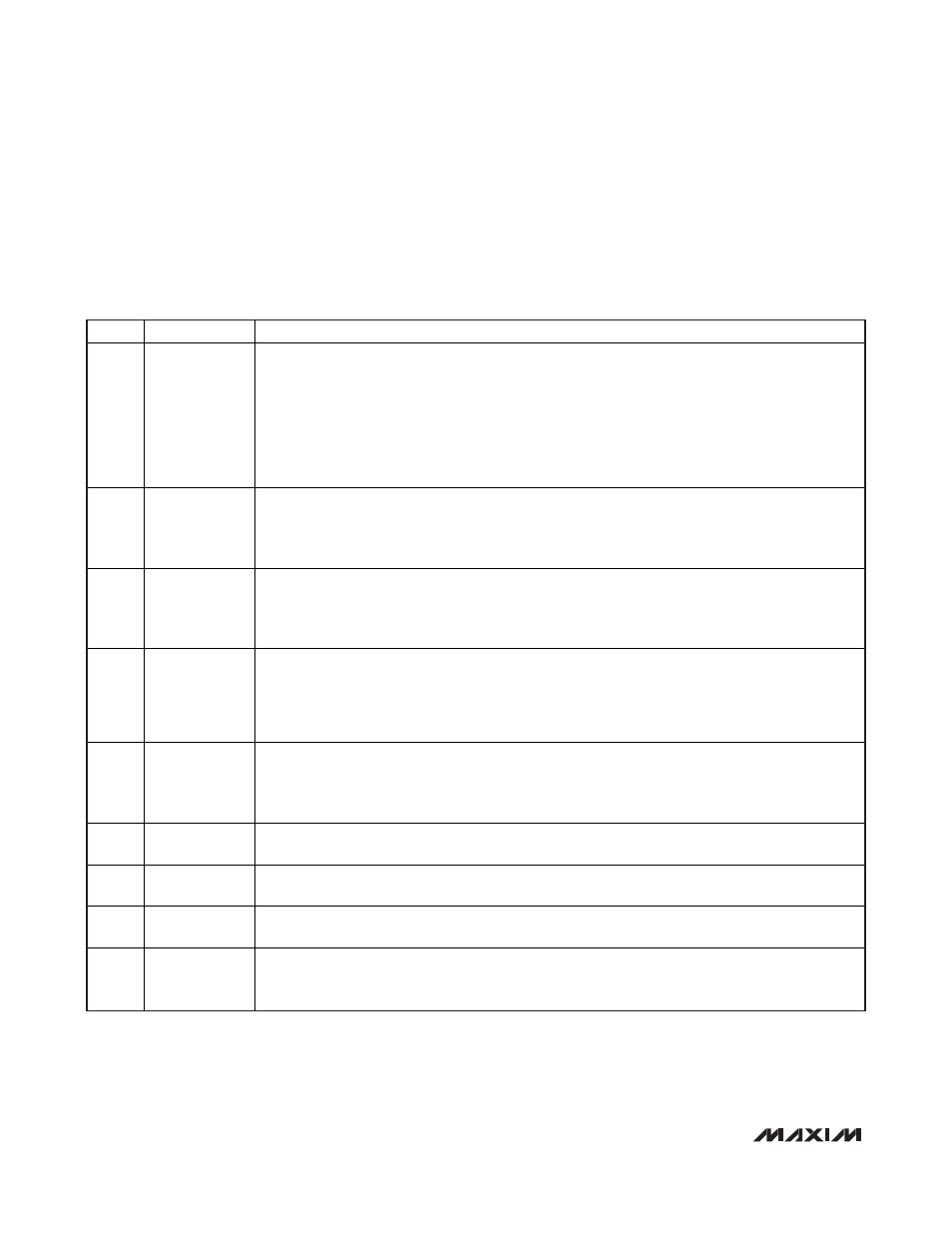

Table 16. MFR_MODE Bit Definition

BIT

BIT NAME

DESCRIPTION

15:8

Input Clock Time

Factor

This is equivalent to the number of external clock cycles provided to CLKIO in 100_S - 2.

MFR_MODE[15:8] = f

EXT_CLK

/10kHz - 2 where f

EXT_CLK

is the frequency of the external clock. For

example, when f

EXT_CLK

= 1MHz, f

EXT_CLK

/10kHz = 100, MFR_MODE[15:8] = 100 – 2 = 98. Valid

external input clock range is from 100kHz (MFR_MODE[15:8] = 8) to 2.5MHz (MFR_MODE[15:8] =

248).

These bits are ignored if internal clock source is selected as the time base (Clock Source Select bit =

0).

7

Clock Out

Enable

The Clock Out Enable bit allows the output of a 1MHz reference clock to CLKIO for synchronizing

multiple MAX16064s.

1 = Enables the 1MHz output on CLKIO.

0 = Reference clock is not output (default).

6

IGNORE_EN

1 = The EN state is ignored and the MAX16064 is controlled according to ON_OFF_CONFIG.

0 = The MAX16064 turns on the external power supplies when EN exceeds its threshold. If EN goes

low after power-up, the MAX16064 turns off a power supply only if MFR_FAULT_RESPONSE[5:4] is

configured to do so.

5

EEPROM Lock

Enable

The EEPROM Lock Enable bit is used to protect external EEPROM data from being overwritten.

1 = The STORE_DEFAULT_ALL command is ignored. The RESTORE_DEFAULT_ALL command is still

valid.

0 = The STORE_DEFAULT_ALL command initiates a store configuration operation to the external

EEPROM attached to A1/SCLE and A2/SDAE (default).

4

Correction

Bypass Enable

Correction Bypass Enable.

1 = Disables a correction algorithm made to voltage and temperature readings.

0 = Applies a correction algorithm to temperature measurement, thus resulting in high-accuracy

readings. For optimal operation, this bit should be cleared to 0 (default).

3

EEPROM Fault

Lock

1 = EEPROM fault locations are locked. If a fault occurs, data is not written to the external EEPROM.

0 = EEPROM fault locations are unlocked. If a fault occurs, data is written to the external EEPROM.

2

PEC Enable

1 = PEC enabled for all commands.

0 = PEC is disabled (default).

1

Filter Setting

1 = Disable filtering of the voltage and temperature conversions.

0 = Enable filtering of the voltage and temperature conversions (default).

0

Clock Source

Select

The Clock Source Select bit determines the MAX16064 reference clock time source.

1 = An external clock must be supplied to CLKIO and is used as the MAX16064 reference clock.

0 = The internal clock is used.

MFR_MODE (D1h)

The MFR_MODE command is used to configure

the MAX16064 to support manufacturer specific

commands. The MFR_MODE command is described

in Table 16.

The default MFR_MODE value is 00h.