Rainbow Electronics MAX9216 User Manual

Page 8

MAX9210/MAX9212/MAX9214/MAX9216/MAX9220/MAX9222

Programmable DC-Balance

21-Bit Deserializers

8

_______________________________________________________________________________________

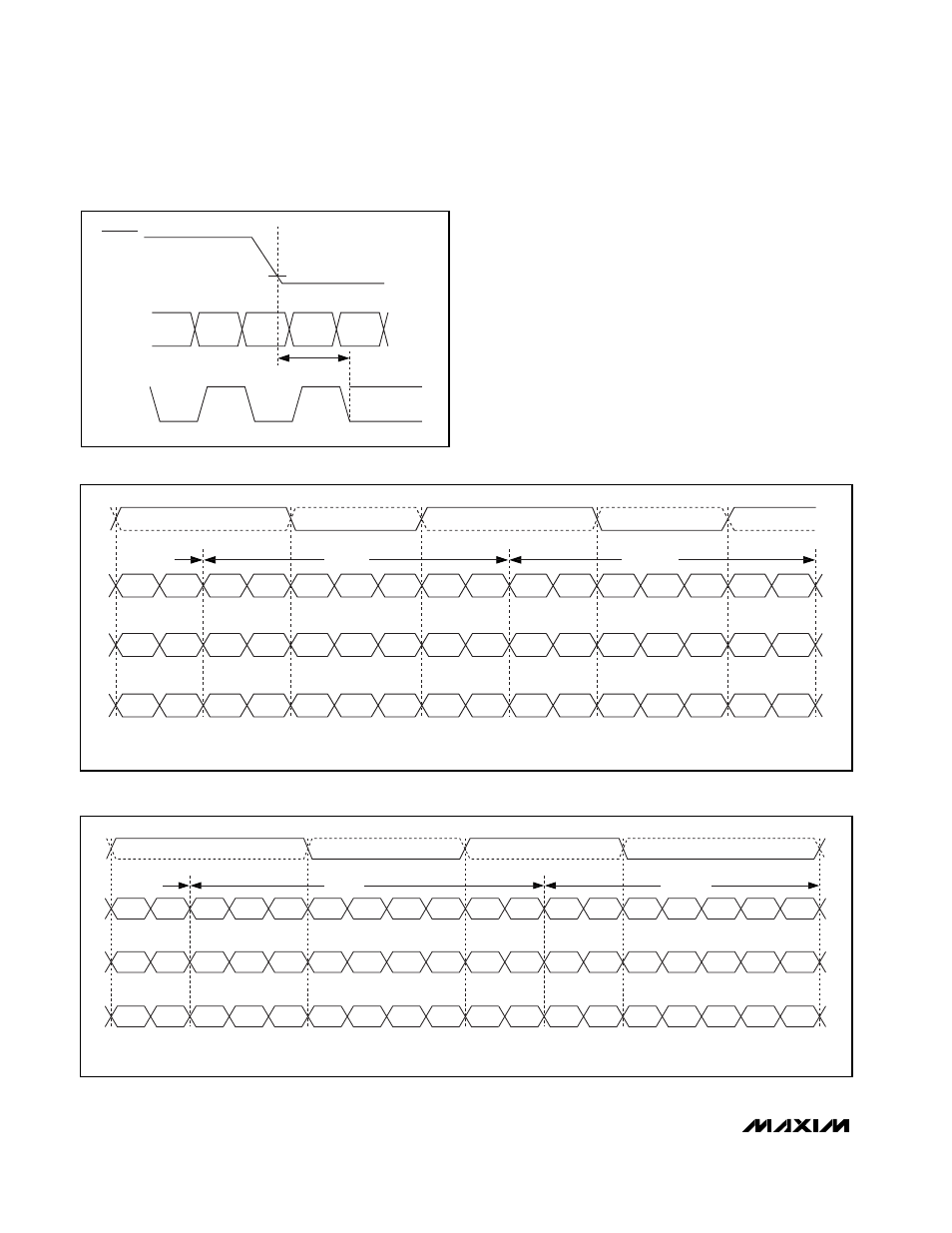

channel is five. Limiting the DSV and choosing the cor-

rect coupling capacitors maintains differential signal

amplitude and reduces jitter due to droop on AC-cou-

pled links.

To obtain DC balance on the data channels, the serial-

izer parallel data is inverted or not inverted, depending

on the sign of the digital sum at the word boundary.

Two complementary bits are appended to each group

of 7 parallel input data bits to indicate to the MAX9210/

MAX9212/MAX9214/MAX9216/MAX9220/MAX9222

deserializers whether the data bits are inverted (see

Figures 9 and 10). The deserializer restores the original

state of the parallel data. The LVDS clock signal alter-

nates duty cycles of 4/9 and 5/9, which maintain DC

balance.

TxIN_ IS DATA FROM THE SERIALIZER.

TxIN1

TxIN7

TxIN8

TxIN14

TxIN15

+

-

CYCLE N + 1

CYCLE N

CYCLE N - 1

TxIN2

TxIN6

TxIN3

TxIN4

TxIN5

TxIN9

TxIN13

TxIN10

TxIN11

TxIN12

TxIN0

TxIN1

TxIN2

TxIN6

TxIN3

TxIN4

TxIN5

TxIN7

TxIN8

TxIN9

TxIN13

TxIN10

TxIN11

TxIN12

TxIN14

TxIN15

TxIN16

TxIN20

TxIN17

TxIN18

TxIN19

TxIN0

TxIN1

TxIN7

TxIN8

TxIN14

TxIN15

TxIN16

TxIN20

TxIN17

TxIN18

TxIN19

TxIN0

RxCLK IN

RxIN1

RxIN0

RxIN2

Figure 9. Deserializer Serial Input in Non-DC-Balanced Mode

TxIN_, DCA_, AND DCB_ ARE DATA FROM THE SERIALIZER.

DCA0

DCB1

DCA1

DCB2

DCA2

CYCLE N + 1

CYCLE N

CYCLE N - 1

TxIN2

TxIN6

TxIN3

TxIN4

TxIN5

TxIN9

TxIN13

TxIN10

TxIN11

TxIN12

TxIN2

TxIN3

TxIN4

DCA0

TxIN5

TxIN6

DCB0

TxIN9

TxIN10

TxIN11

DCA1

TxIN12

TxIN13

DCB1

TxIN16

TxIN17

TxIN18

DCA2

TxIN19

TxIN20

DCB2

TxIN0

TxIN1

TxIN7

TxIN8

TxIN14

TxIN15

TxIN16

TxIN20

TxIN17

TxIN18

TxIN19

DCB0

RxCLK IN

RxIN1

RxIN0

RxIN2

TxIN1

TxIN8

TxIN15

TxIN0

TxIN7

TxIN14

+

-

Figure 10. Deserializer Serial Input in DC-Balanced Mode

0.8V

PWRDWN

RxCLK IN

RxOUT_

RxCLK OUT

RPDD

HIGH-Z

Figure 8. Power-Down Delay