Rainbow Electronics MAX9216 User Manual

Page 10

MAX9210/MAX9212/MAX9214/MAX9216/MAX9220/MAX9222

Programmable DC-Balance

21-Bit Deserializers

10

______________________________________________________________________________________

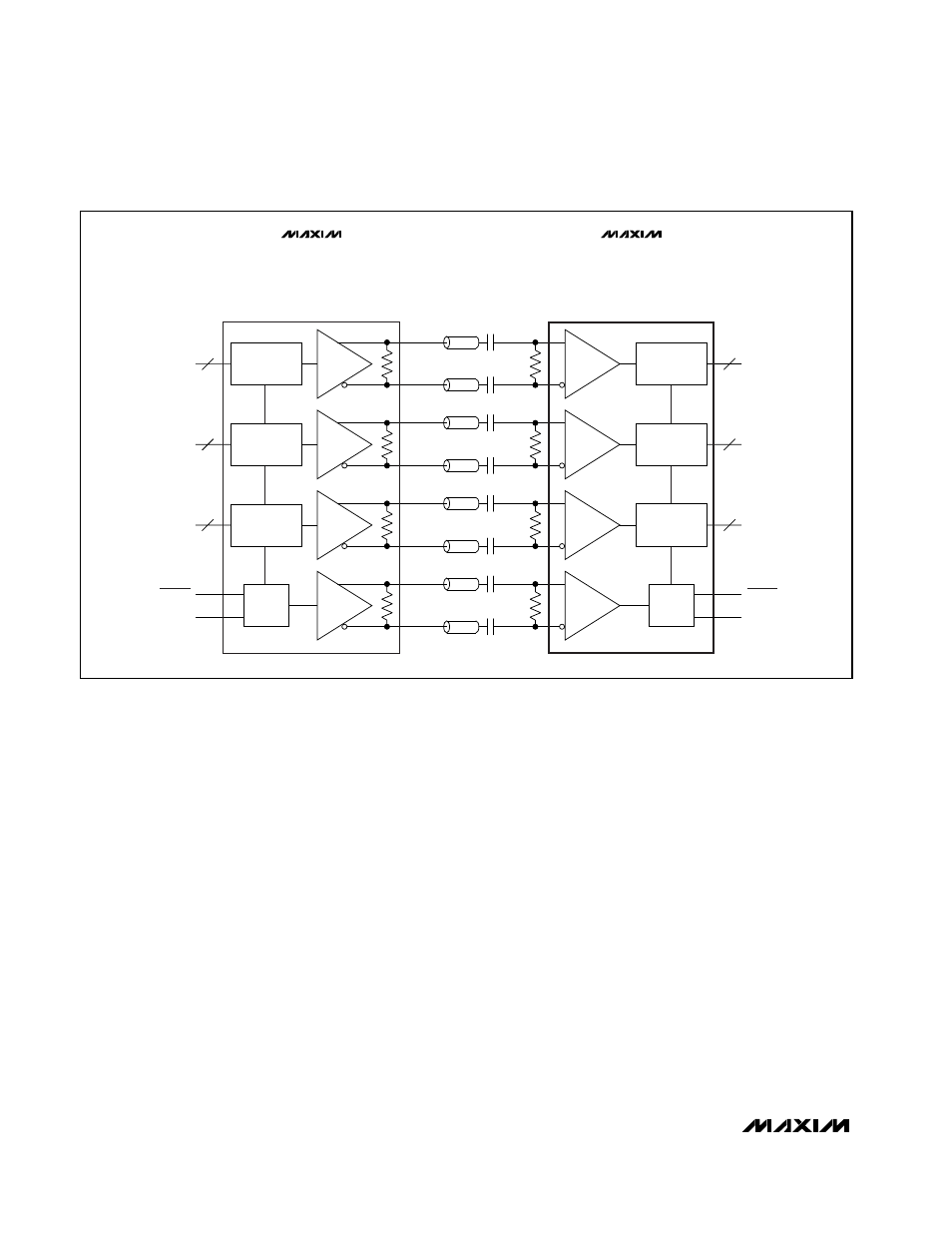

The RC network for an AC-coupled link consists of the

LVDS receiver termination resistor (R

T

), the LVDS driver

output resistor (R

O

), and the series AC-coupling capac-

itors (C). The RC time constant for two equal-value

series capacitors is (C x (R

T

+ R

O

))/2 (Figure 12). The

RC time constant for four equal-value series capacitors

is (C x (R

T

+ R

O

))/4 (Figure 13).

R

T

is required to match the transmission line imped-

ance (usually 100

Ω) and R

O

is determined by the LVDS

driver design (the minimum differential output resis-

tance of 78

Ω for the MAX9209/MAX9211/MAX9213/

MAX9215 serializers is used in the following example).

This leaves the capacitor selection to change the sys-

tem time constant.

In the following example, the capacitor value for a

droop of 2% is calculated. Jitter due to this droop is

then calculated assuming a 1ns transition time:

C = - (2 x t

B

x DSV) / (ln (1 - D) x (R

T

+ R

O

)) (Eq 1)

where:

C = AC-coupling capacitor (F)

t

B

= bit time (s)

DSV = digital sum variation (integer)

ln = natural log

D = droop (% of signal amplitude)

R

T

= termination resistor (

Ω)

R

O

= output resistance (

Ω)

Equation 1 is for two series capacitors (Figure 12). The

bit time (t

B

) is the period of the parallel clock divided by

9. The DSV is 10. See equation 3 for four series capaci-

tors (Figure 13).

The capacitor for 2% maximum droop at 8MHz parallel

rate clock is:

C = - (2 x t

B

x DSV) / (ln (1 - D) x (R

T

+ R

O

))

C = - (2 x 13.9ns x 10) / (ln (1 - 0.02) x (100

Ω + 78Ω))

C = 0.0773µF

(7 + 2):1

1:(9 - 2)

7

7

100

Ω

(7 + 2):1

1:(9 - 2)

7

7

100

Ω

(7 + 2):1

1:(9 - 2)

7

7

100

Ω

PLL

PLL

100

Ω

MAX9209

MAX9211

MAX9213

MAX9215

MAX9210

MAX9212

MAX9214

MAX9216

MAX9220

MAX9222

TxOUT

TxCLK OUT

RxIN

RxCLK IN

21:3 SERIALIZER

3:21 DESERIALIZER

PWRDWN

RxCLK OUT

RxOUT

PWRDWN

TxCLK IN

TxIN

HIGH-FREQUENCY, CERAMIC

SURFACE-MOUNT CAPACITORS

CAN ALSO BE PLACED AT THE

SERIALIZER INSTEAD OF THE DESERIALIZER.

Figure 12. Two Capacitors per Link, AC-Coupled, DC-Balanced Mode