Timer 1 control register 1 (t1c1) – Rainbow Electronics T48C862-R8 User Manual

Page 42

42

T48C862-R8

4590B–4BMCU–02/03

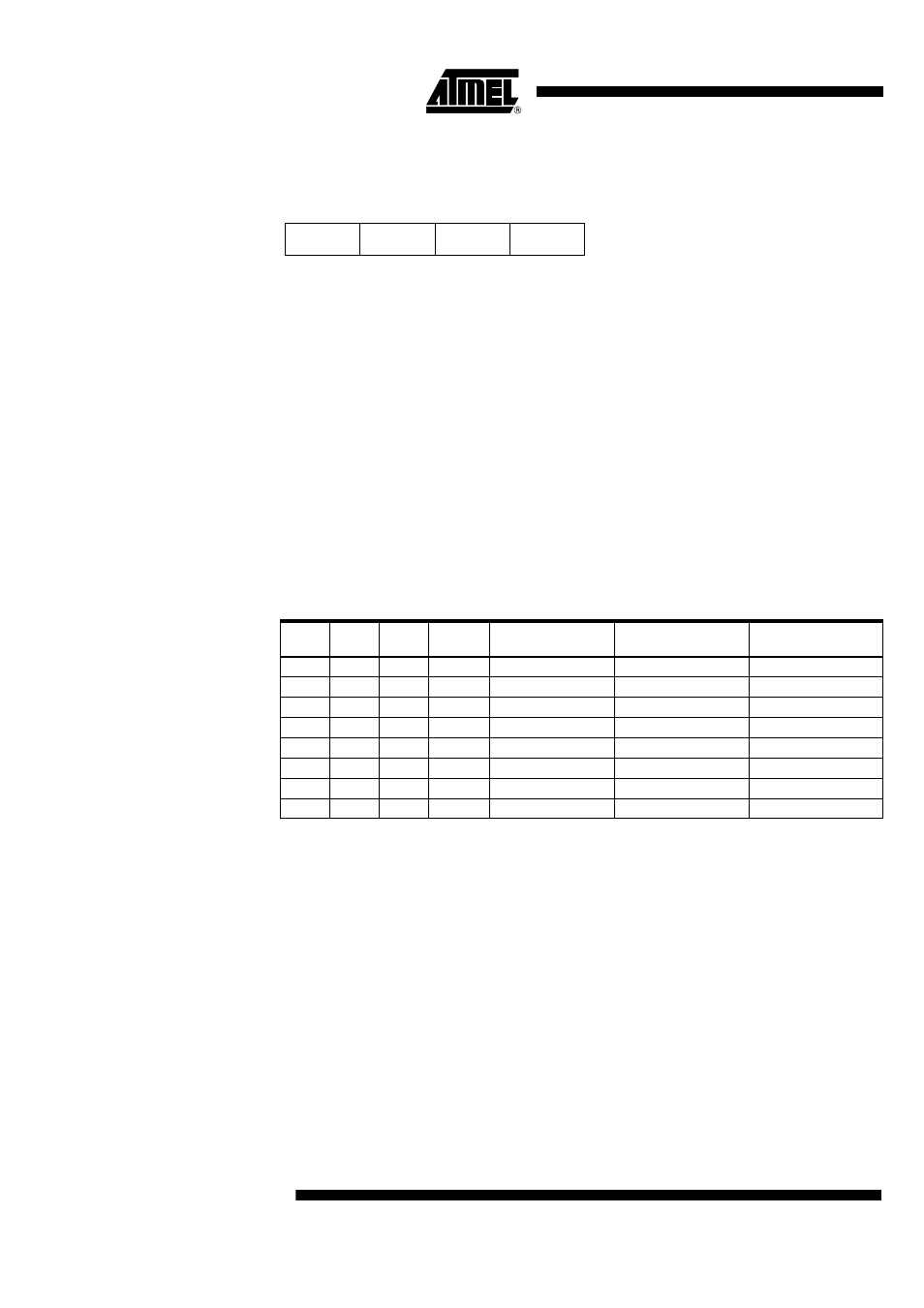

Timer 1 Control Register 1

(T1C1)

Address: "7"hex - Subaddress: "8"hex

* Bit 3 -> MSB, Bit 0 -> LSB

The three bits T1C[2:0] select the divider for timer 1. The resulting time interval depends

on this divider and the timer 1 input clock source. The timer input can be supplied by the

system clock, the 32-kHz oscillator or via the clock management. If the clock manage-

ment generates the SUBCL, the selected input clock from the RC oscillator, 4-MHz

oscillator or an external clock is divided by 16.

Bit 3 *

Bit 2

Bit 1

Bit 0

T1RM

T1C2

T1C1

T1C0

Reset value: 1111b

T1RM

T

imer

1

R

estart

M

ode T1RM = 0, write access without Timer 1 restart

T1RM = 1, write access with Timer 1 restart

Note:

If WDL = 0, Timer 1 restart is impossible

T1C2

T

imer

1 C

ontrol bit

2

T1C1

T

imer

1 C

ontrol bit

1

T1C0

T

imer

1 C

ontrol bit

0

T1C2

T1C1

T1C0

Divider

Time Interval with

SUBCL

Time Interval with

SUBCL = 32 kHz

Time Interval with

SYSCL = 2/1 MHz

0

0

0

2

SUBCL/2

61 µs

1 µs/2 µs

0

0

1

4

SUBCL/4

122 µs

2 µs/4 µs

0

1

0

8

SUBCL/8

244 µs

4 µs/8 µs

0

1

1

16

SUBCL/16

488 µs

8 µs/16 µs

1

0

0

32

SUBCL/32

0.977 ms

16 µs/32 µs

1

0

1

256

SUBCL/256

7.812 ms

128 µs/256 µs

1

1

0

2048

SUBCL/2048

62.5 ms

1024 µs/2048 µs

1

1

1

16384

SUBCL/16384

500 ms

8192 µs/16384 µs