Addsub – Xilinx V2.1 User Manual

Page 83

Math

83

Xilinx Blocks

%XILINX%\coregen\ip\xilinx\eip1\com\xilinx\ip\baseblox_v5_0\do

c\accum.pdf

AddSub

The Xilinx AddSub block implements an adder/subtractor.

The operation can be fixed (Add or Subtract) or changed

dynamically under control of the

sub

mode signal.

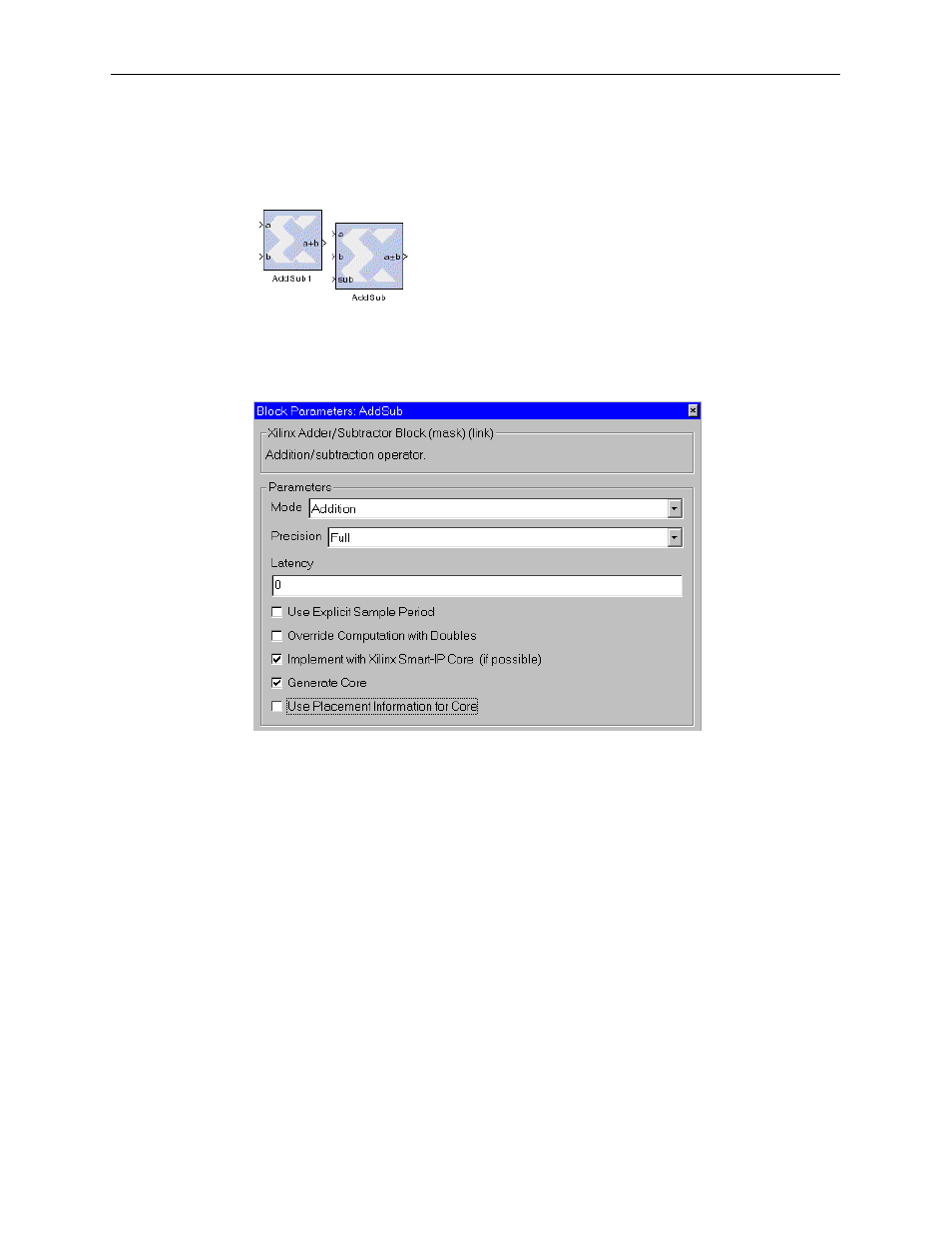

Block Parameters Dialog Box

The block parameters dialog box can be invoked by double-clicking the icon in your

Simulink model.

Figure 3-55: AddSub block parameters dialog box

Parameters specific to the AddSub block are:

•

Mode

: specifies the block operation to be Addition, Subtraction, or Addition/

Subtraction. When Addition/Subtraction is selected, the block operation is

determined by the

sub

input port, which must be driven by a 1-bit unsigned

signal. When the

sub

input is 1, the block performs subtraction. Otherwise, it

performs addition.

•

Implement with Xilinx Smart-IP Core

: when checked, the System

Generator will implement the block as a LogiCORE. Otherwise, it is implemented

as a synthesizable VHDL module.

Other parameters used by this block are explained in the Common Parameters section

of the previous chapter.

Xilinx LogiCORE

If the

Implement with Xilinx Smart-IP Core

checkbox is selected on the

parameters dialog box, and if the output width is in the range of 1 to 256, the block