Xilinx V2.1 User Manual

Page 65

Communication

65

Xilinx Blocks

Block Interface

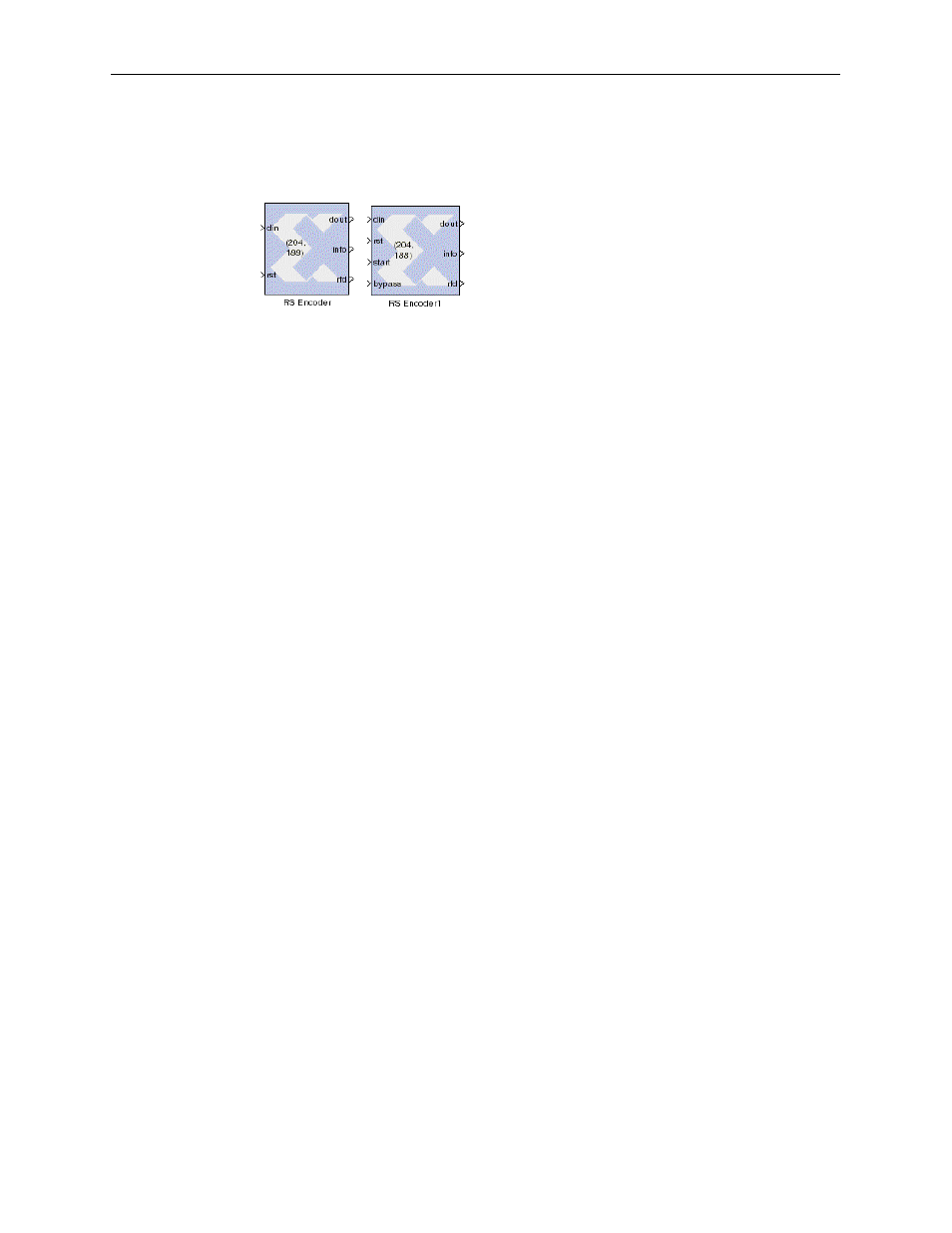

The Xilinx RS Encoder block has two inputs (

din, rst

) and three output (

dout,

info and rfd

) ports. The RS Encoder block also has optional

start

and

bypass

input ports.

Figure 3-43: Reed-Solomon Encoder icons, including optional ports

The port descriptions are:

•

din

: carries the input information symbols of the RS code. The

din

signal must

be an

UFixS_0

where S is equal to the symbol width (3 to 12).

•

rst

: carries the reset signal for the RS encoder. After the

rst

signal is asserted the

RS encoder initializes the next available input as the first information symbol. The

rst

signal must be a

UFix1_0

.

•

start

: when start is asserted for a particular sample period, the data on the din

port is taken as the first input information symbol. If start is asserted high for

more than one sample period, the data at the last sample period is taken as the

first input information symbol. The start signal is ignored if bypass is asserted

high for the same sample period. The start signal always resets the state of the

code generator. The start signal must be a

UFix1_0

.

•

bypass

: when bypass is asserted for a particular sample period, the

corresponding data input on the din port is passed straight through to the dout

port with a 4 (6 in case of CCSDS) sample period delay. The bypass signal has no

effect on the state of the code generator. The bypass signal must be a

UFix1_0

.

•

dout

: carries the input information symbols and the parity symbols of the RS

code. The

dout

signal has the same arithmetic type as the

din

input.

•

info

: The

info

output is 1 when there is information symbols on the dout port.

The info output is also 1 when the bypass asserted input data appears at the dout

port. The info signal is a

UFix1_0

.

•

rfd

: carries the ready for data signal for the RS encoder. This signal is 1 till the RS

encoder is accepting information symbols and 0 when the RS encoder is

outputting parity symbols. The

rfd

signal is a

UFix1_0

.