Xilinx V2.1 User Manual

Page 113

Memory

113

Xilinx Blocks

Xilinx LogiCORE

The block always uses a Xilinx LogiCORE Single Port Block Memory V3.2 or

Distributed Memory V5.0. For the block memory, the address width must be equal to

where d denotes the memory depth.

The tables below show the width that is acceptable for each depth.

When distributed memory parameter is selected, the memory depth must be between

16 and 65536, inclusive for Virtex-II and 16 to 4096, inclusive for the FPGA families.

The word width must be between 1 and 1024, inclusive.

The Core datasheet for the Single Port Block Memory can be found locally at:

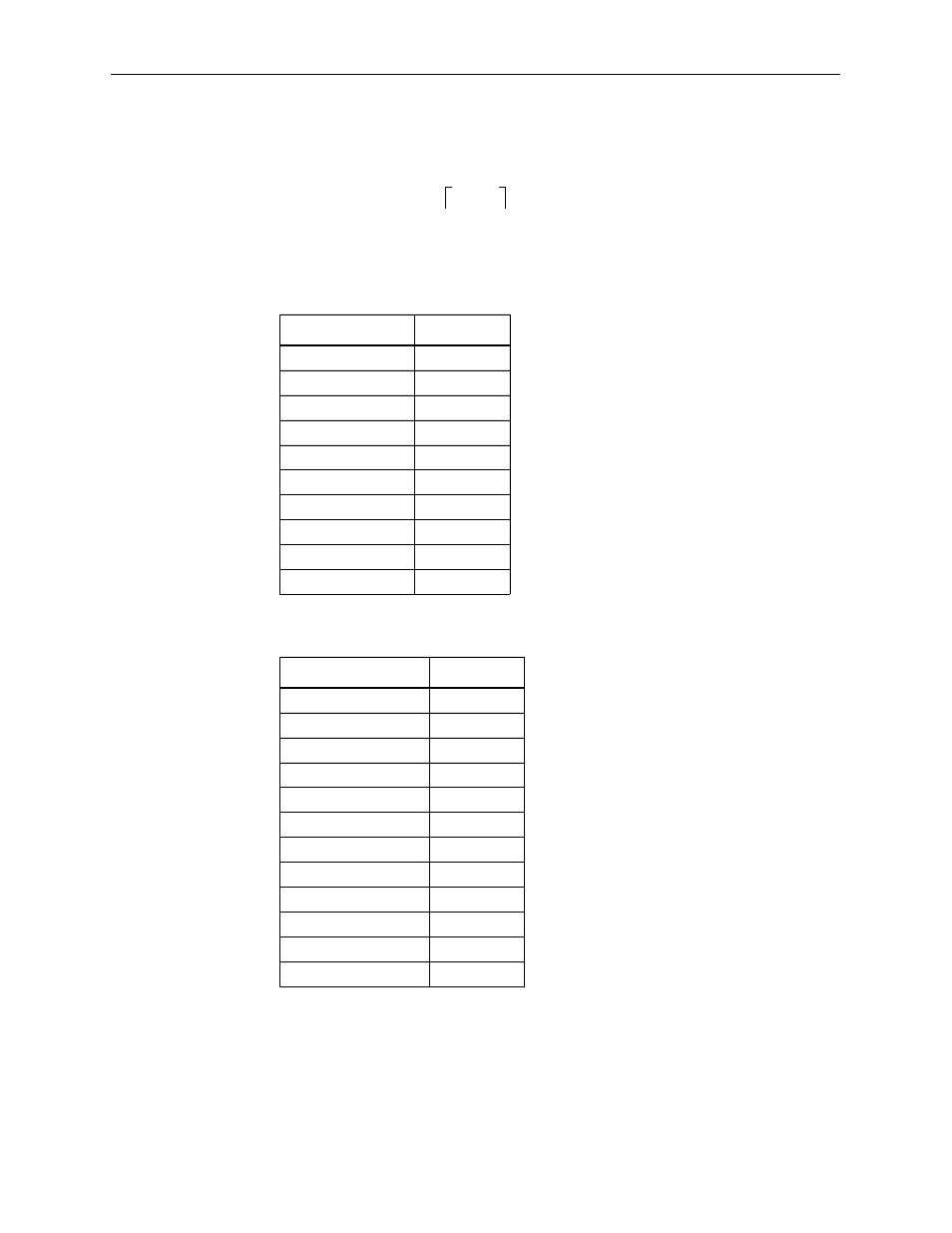

Table: Maximum Word Width for Various Depth Ranges (Virtex/Virtex-E)

Depth

Width

2 to 512

256

513 to 1024

256

1025 to 2048

256

2049 to 4096

192

4097 to 8192

96

8193 to 16K

48

16K+1 to 32K

24

32K+1 to 64K

12

64K+1 to 128K

6

128K+1 to 256K

3

Table: Maximum Word Width for Various Depth Ranges (Virtex-II)

Depth

Width

2 to 512

256

513 to 1024

256

1025 to 2048

256

2049 to 4096

256

4097 to 8192

256

8193 to 16K

192

16K+1 to 32K

96

32K+1 to 64K

48

64K+1 to 128K

24

128K+1 to 256K

12

256K+1 to 512K

6

512K+1 to 1024K

3

d

2

log