Concat – Xilinx V2.1 User Manual

Page 30

30

Xilinx Development System

Xilinx System Generator v2.1 Reference Guide

input and output ports respectively. To configure the black box, enter the parameters

in the black box block parameters dialog box as shown in the figure below.

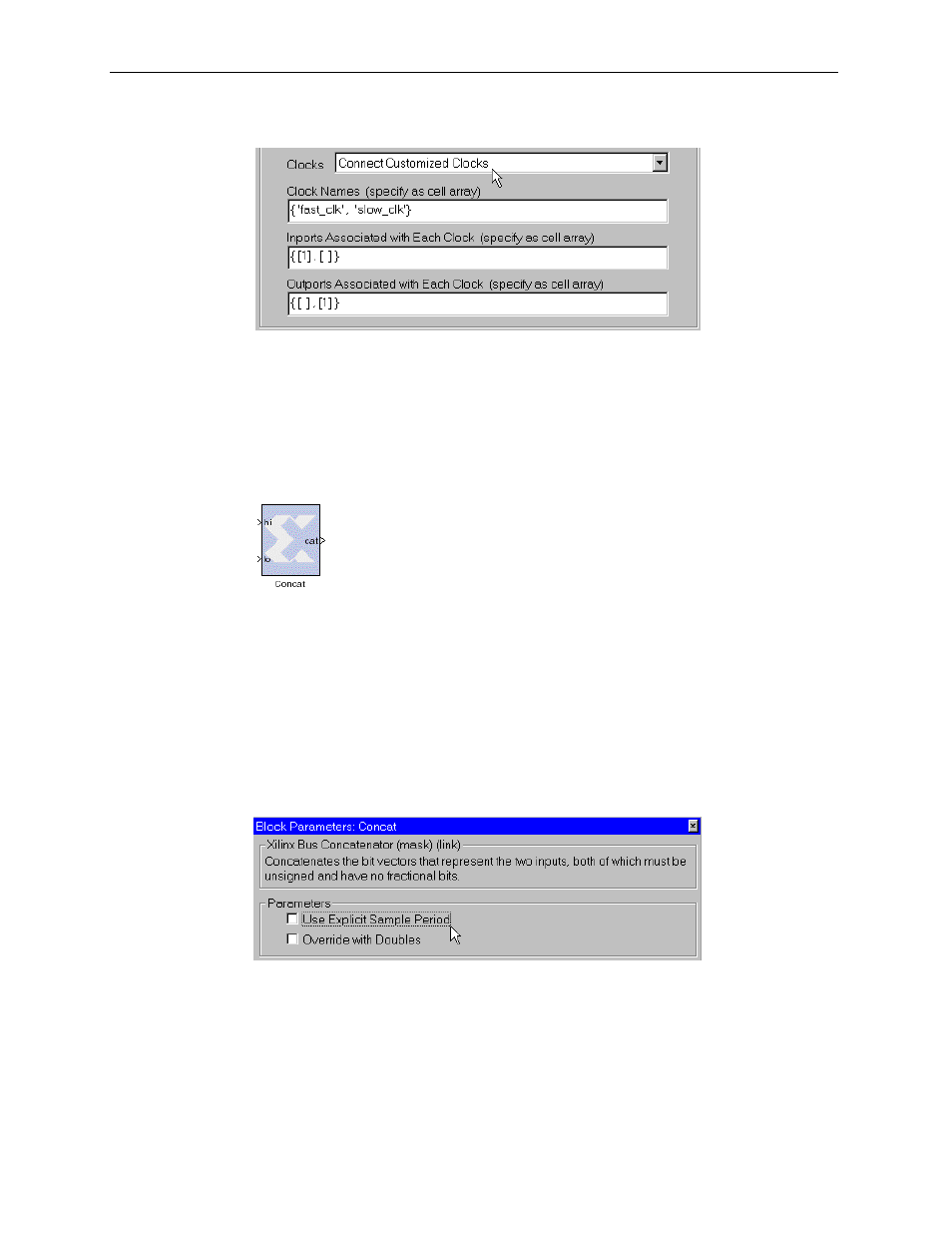

Figure 3-4: Customizing Clocks in the Black Box block parameters dialog box

These settings indicate that the black box should have clocks named

fast_clk

and

slow_clk

. The

fast_clk

should have the same frequency as the samples presented

to input port #1, and the

slow_clk

should have the same frequency as output port

#1.

Concat

The Xilinx Concat block performs a concatenation of two bit vectors

represented by unsigned integer numbers, i.e. two unsigned numbers

with binary points at position zero.

The Xilinx Reinterpret block provides capabilities that can extend the

functionality of the Concat block.

Block Interface

The block has two input ports and one output port. The two input ports are labeled

hi

and

low

. The number input to the

hi

port will occupy the most significant bits of

the output and the number that is input to the

low

port will occupy the least

significant bits of the output.

Block Parameters Dialog Box

The block parameters dialog box can be invoked by double-clicking the icon in your

Simulink model.

Figure 3-5: Concat block parameters dialog box

Parameters used by this block are explained in the Common Parameters section of the

previous chapter.

The Concat block does not use a Xilinx LogiCORE.