Spartan-6 xc6slx45t-3fgg484 fpga, Configuration – Xilinx SP605 User Manual

Page 14

14

SP605 Hardware User Guide

UG526 (v1.8) September 24, 2012

Chapter 1: SP605 Evaluation Board

1. Spartan-6 XC6SLX45T-3FGG484 FPGA

A Xilinx Spartan-6 XC6SLX45T-3FGG484 FPGA is installed on the SP605 Evaluation Board.

References

See the Spartan-6 FPGA Data Sheet.

Configuration

The SP605 supports configuration in the following modes:

•

JTAG (using the included USB-A to Mini-B cable)

•

JTAG (using System ACE CF and CompactFlash card)

•

Master SPI x4

•

Master SPI x4 with off-board device

•

Linear BPI Flash

For details on configuring the FPGA, see

Mode switch SW1 (see

) is set to 10 = Slave SelectMAP to choose the

System ACE CF default configuration.

16

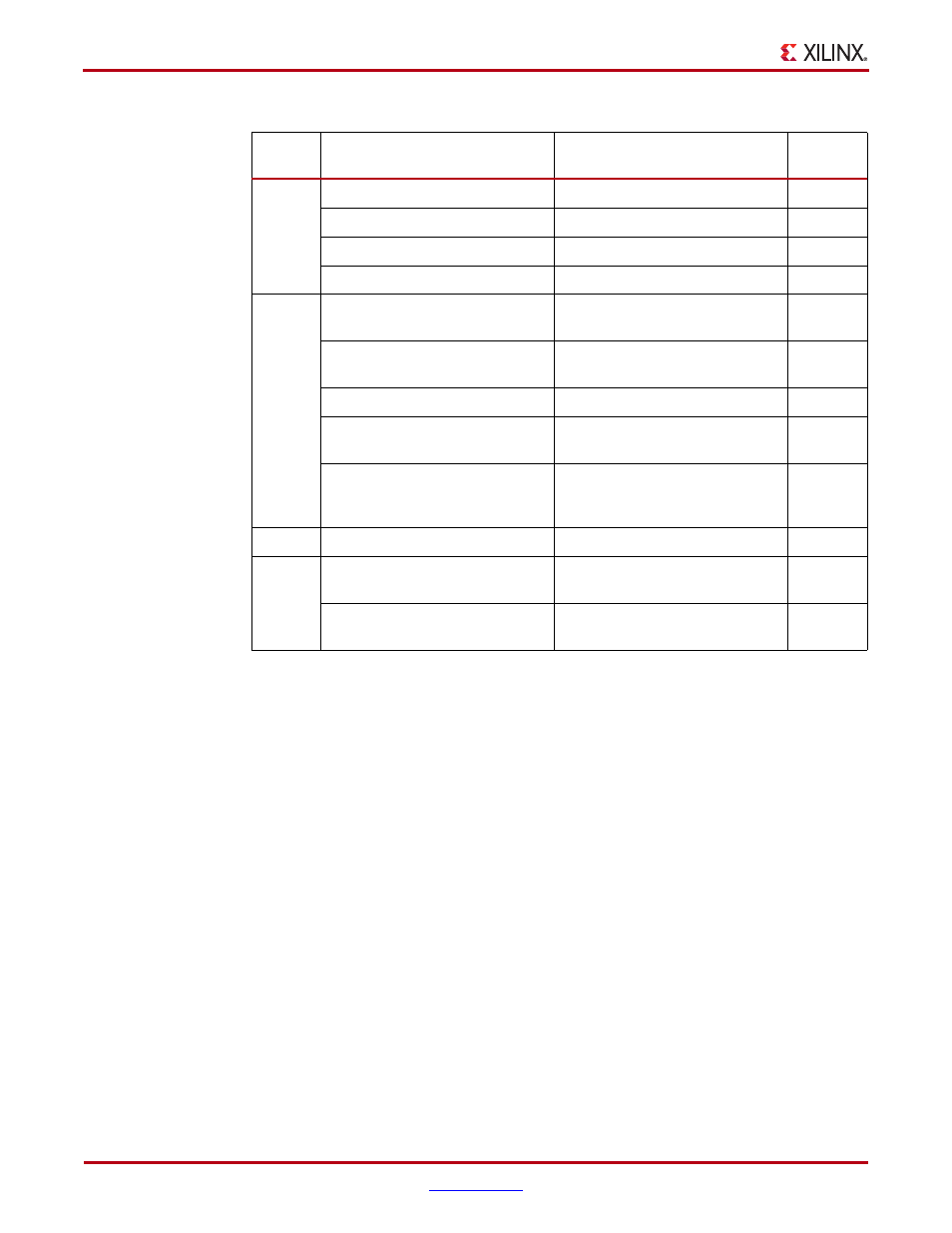

a. User LEDs (4)

Red LEDs (active-High)

14

b. User Pushbuttons (4)

Active-High

14

c. User DIP Switch (4-pole)

4-pole (active-High)

14

d. User SMA (2)

GPIO x2 SMA

13

17

Switches

Power, Configuration,

Pushbutton Switches

14, 18, 20,

25

a. SP605 Power On-Off Slide

Switch

25

b. FPGA Mode DIP Switch

18

c. System ACE CF

Configuration DIP Switch

20

d. FPGA PROG, CPU Reset,

and System ACE CF Reset

Pushbutton Switches

14, 20

18

FMC LPC Connector

Samtec ASP-134603-01

10

19

a. Power Management

Controller

2x TI UCD9240PFC

21, 26

b. Mini-Fit Type 6-Pin, ATX

Type 4-pin

12V input power connectors

25

Table 1-1:

SP605 Features (Cont’d)

Number

Feature

Notes

Schematic

Page