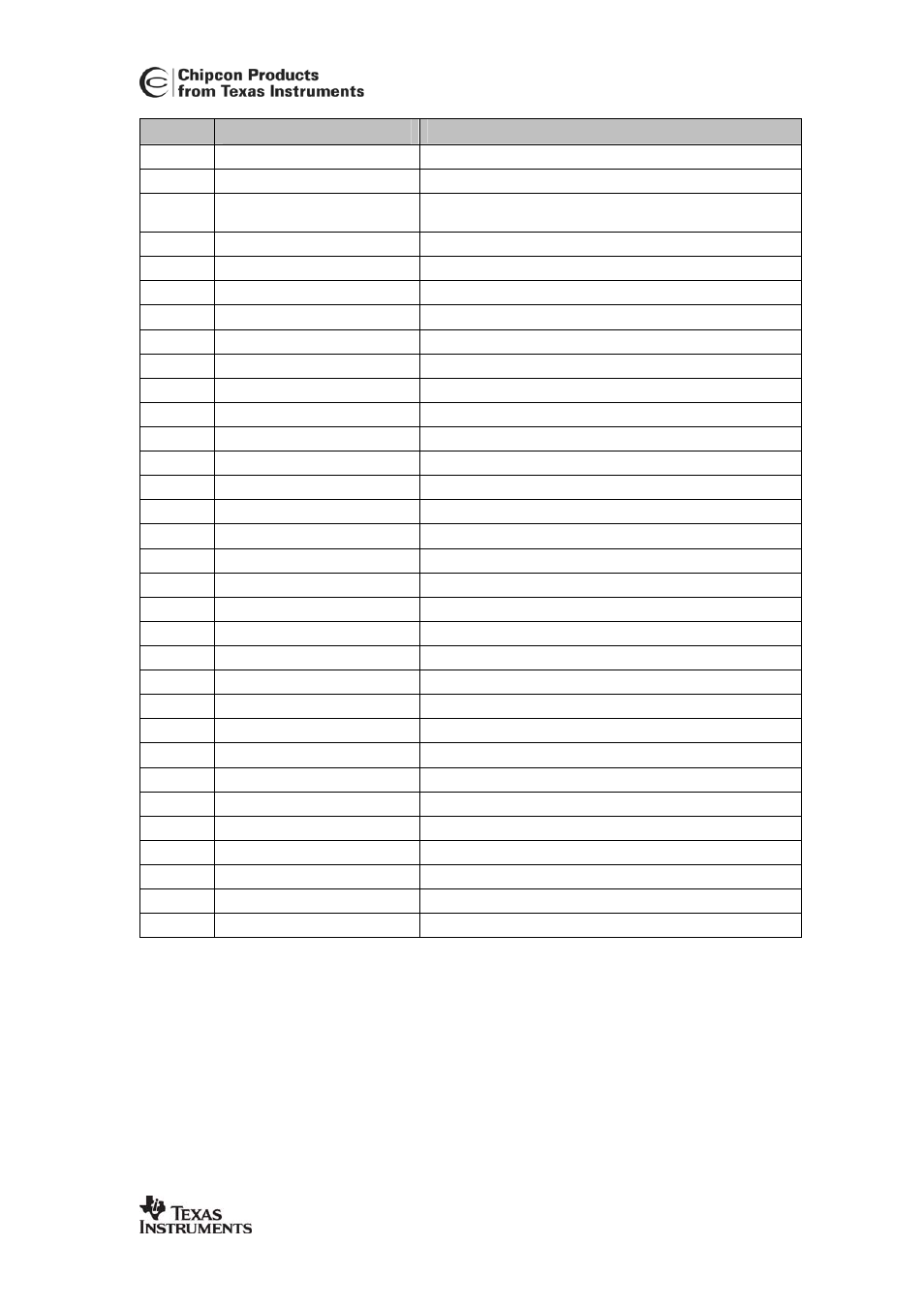

Table 13, Cc2420 – Texas Instruments 3138 155 232931 User Manual

Page 82

CC2420

SWRS041B Page 82 of 89

SFDMUX

Signal output on SFD pin

Description

0 SFD

Normal

operation

1

ADC_I[0]

ADC, I-branch, LSB used for random number generation

2

DEMOD_RESYNCH_EARLY

High one 16 MHz clock cycle each time the demodulator

resynchronises early

3

LOCK_STATUS

Lock status, same as FSCTRL.LOCK_STATUS

4

MOD_CHIP

Chip rate data signal during transmission

5 MOD_SERIAL_DATA_OUT

Bit

rate data signal during transmission

6 FFCTRL_FS_PD

Frequency

synthesizer power down, active high

7

FFCTRL_ADC_PD

ADC power down, active high

8

FFCTRL_VGA_PD

VGA power down, active high

9

FFCTRL_RXBPF_PD

Receiver bandpass filter power down, active high

10

FFCTRL_LNAMIX_PD

Receiver LNA / Mixer power down, active high

11

FFCTRL_PA_P_PD

Power amplifier power down, active high

12

VGA_PEAK_DET[0]

VGA Peak detector, gain stage 0

13

VGA_PEAK_DET[2]

VGA Peak detector, gain stage 2

14

VGA_PEAK_DET[4]

VGA Peak detector, gain stage 4

15 AGC_LNAMIX_GAINMODE[0]

RF

receiver front-end gain mode, bit 0

16

AGC_VGA_GAIN[0]

VGA gain setting, bit 0

17 RXBPF_CAL_CLK

Receiver

bandpass filter calibration clock

18 -

Reserved

19 -

Reserved

20 -

Reserved

21 -

Reserved

22 -

Reserved

23 -

Reserved

24

PD_F_COMP

Frequency synthesizer frequency comparator value

25 FSDIG_FREF

Frequency

synthesizer, 4 MHz reference signal

26 FSDIG_FPLL

Frequency

synthesizer, 4 MHz divided signal

27 FSDIG_LOCK_WINDOW Frequency

synthesizer, lock window

28

WINDOW_SYNC

Frequency synthesizer, synchronized lock window

29

CLK_ADC_DIG

ADC clock signal 2

30 ZERO

Low

31 ONE

High

Table 13. SFD test signal select table