Digital inputs/outputs, Cc2420 – Texas Instruments 3138 155 232931 User Manual

Page 12

CC2420

SWRS041B Page 12 of 89

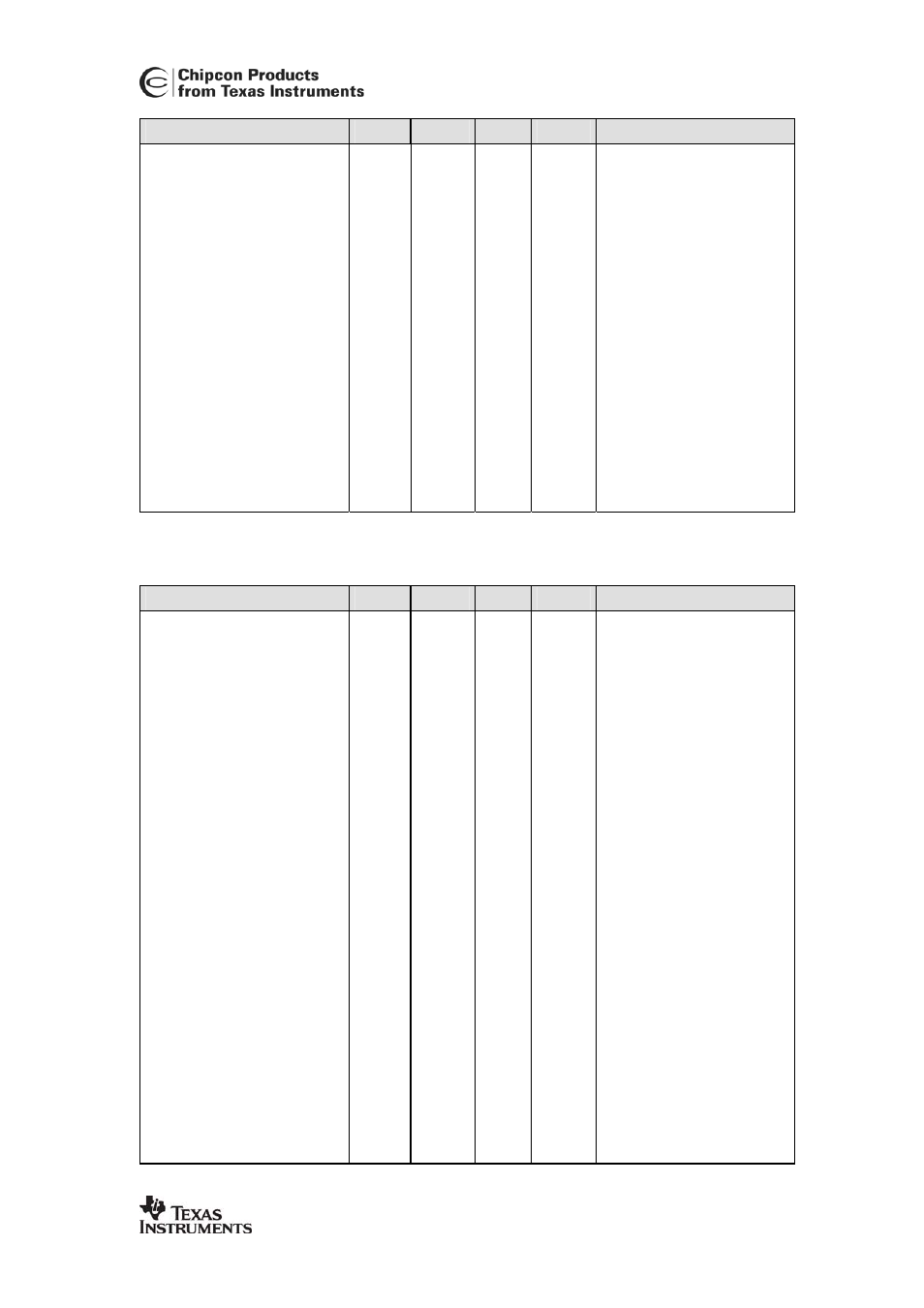

Parameter

Min.

Typ.

Max.

Unit

Condition / Note

Crystal load capacitance

12 16 20 pF

16 pF recommended

Crystal ESR

60

Ω

Crystal oscillator start-up time

1.0

ms

16 pF load

Phase noise

−109

−117

−117

−117

dBc/Hz

dBc/Hz

dBc/Hz

dBc/Hz

Unmodulated carrier

At ±1 MHz offset from carrier

At ±2 MHz offset from carrier

At ±3 MHz offset from carrier

At ±5 MHz offset from carrier

PLL loop bandwidth

100

kHz

PLL lock time

192

µs

The startup time from the crystal

oscillator is running and RX / TX

turnaround time

6.7 Digital

Inputs/Outputs

Parameter

Min.

Typ.

Max.

Unit

Condition / Note

General

Signal levels are referred to the

voltage level at pin DVDD3.3

Logic "0" input voltage

0 0.3*

DVDD

V

Logic "1" input voltage

0.7*

DVDD

DVDD

V

Logic "0" output voltage

0

0.4

V

Output

current

−8 mA,

3.3 V supply voltage

Logic "1" output voltage

2.5

VDD

V

Output current 8 mA,

3.3 V supply voltage

Logic "0" input current

NA

−1

µA

Input signal equals GND

Logic "1" input current

NA

1

µA

Input signal equals VDD

FIFO

setup time

20

ns

TX unbuffered mode, minimum

time FIFO must be ready before

the positive edge of FIFOP

FIFO

hold time

10

ns

TX unbuffered mode, minimum

time FIFO must be held after the

positive edge of FIFOP

Serial interface pins (SCLK, SI, SO

and CSn) timing specification