Configuration registers, Cc2420, 37 configuration registers – Texas Instruments 3138 155 232931 User Manual

Page 61

CC2420

SWRS041B Page 61 of 89

37 Configuration Registers

The configuration of

CC2420

is done by

programming the 16-bit configuration

registers. Complete descriptions of the

registers are given in the following tables.

After chip reset (from the RESETn pin or

programmable through the MAIN.RESETn

configuration bit), all the registers have

default values as shown in the tables.

Note that the MAIN register is only reset

by using the pin reset RESETn. When

writing to this register, all bits will get the

value written, not the default value. This

also means that the MAIN.RESETn bit

must be written both low and then high to

perform a chip reset through the serial

interface.

15 registers are Strobe Command

Registers, listed first in Table 11 below.

Accessing these registers will initiate the

change of an internal state or mode. There

are 33 normal 16-bits registers, also listed

in Table 11. Many of these registers are

for test purposes only, and need not be

accessed for normal operation of

CC2420

.

The FIFOs are accessed through two 8-bit

registers, TXFIFO and RXFIFO. The

TXFIFO

register is write only. Data may

still be read out of the TXFIFO through

regular RAM access (see section RAM

access section on page 29), but data is

then not removed from the FIFO. Note that

the crystal oscillator must be active for all

FIFO and RAM access.

During address transfer, and while data is

being written to the TXFIFO, a status byte

is returned on the serial data output pin

SO

. This status byte is described in Table

All configuration and status registers are

described in the tables following Table 11.

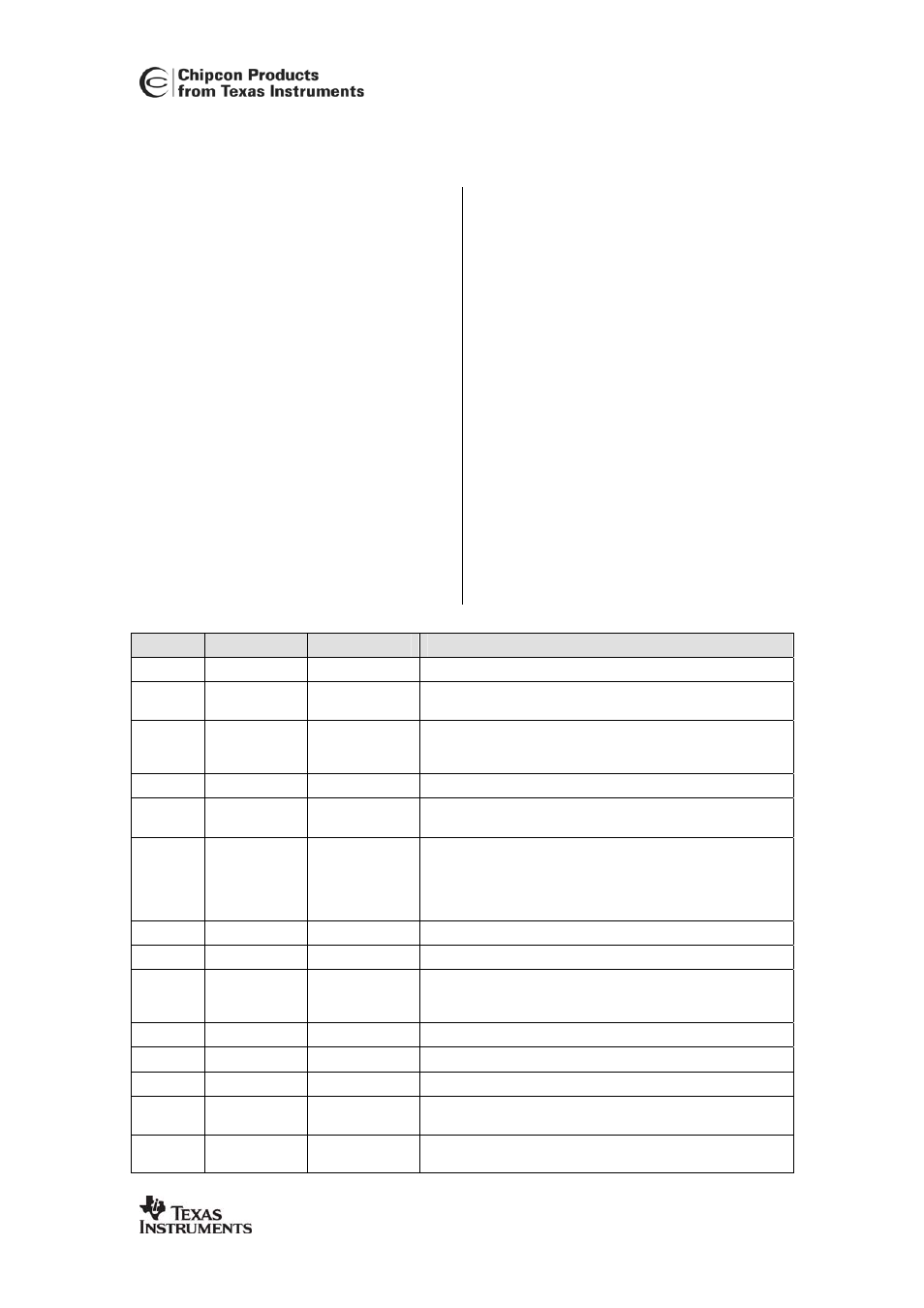

Address

Register

Register type

Description

0x00

SNOP

S

No Operation (has no other effect than reading out status-bits)

0x01

SXOSCON

S

Turn on the crystal oscillator (set XOSC16M_PD = 0 and

BIAS_PD = 0)

0x02

STXCAL

S

Enable and calibrate frequency synthesizer for TX;

Go from RX / TX to a wait state where only the synthesizer is

running.

0x03

SRXON

S Enable

RX

0x04

STXON

S

Enable TX after calibration (if not already performed)

Start TX in-line encryption if SPI_SEC_MODE

≠ 0

0x05

STXONCCA

S

If CCA indicates a clear channel:

Enable calibration, then TX.

Start in-line encryption if SPI_SEC_MODE

≠ 0

else

do nothing

0x06

SRFOFF

S

Disable RX/TX and frequency synthesizer

0x07

SXOSCOFF

S

Turn off the crystal oscillator and RF

0x08

SFLUSHRX

S

Flush the RX FIFO buffer and reset the demodulator. Always

read at least one byte from the RXFIFO before issuing the

SFLUSHRX

command strobe

0x09

SFLUSHTX

S

Flush the TX FIFO buffer

0x0A

SACK

S

Send acknowledge frame, with pending field cleared.

0x0B

SACKPEND

S

Send acknowledge frame, with pending field set.

0x0C

SRXDEC

S

Start RXFIFO in-line decryption / authentication (as set by

SPI_SEC_MODE)

0x0D

STXENC

S

Start TXFIFO in-line encryption / authentication (as set by

SPI_SEC_MODE), without starting TX.