Cc2420 – Texas Instruments 3138 155 232931 User Manual

Page 78

CC2420

SWRS041B Page 78 of 89

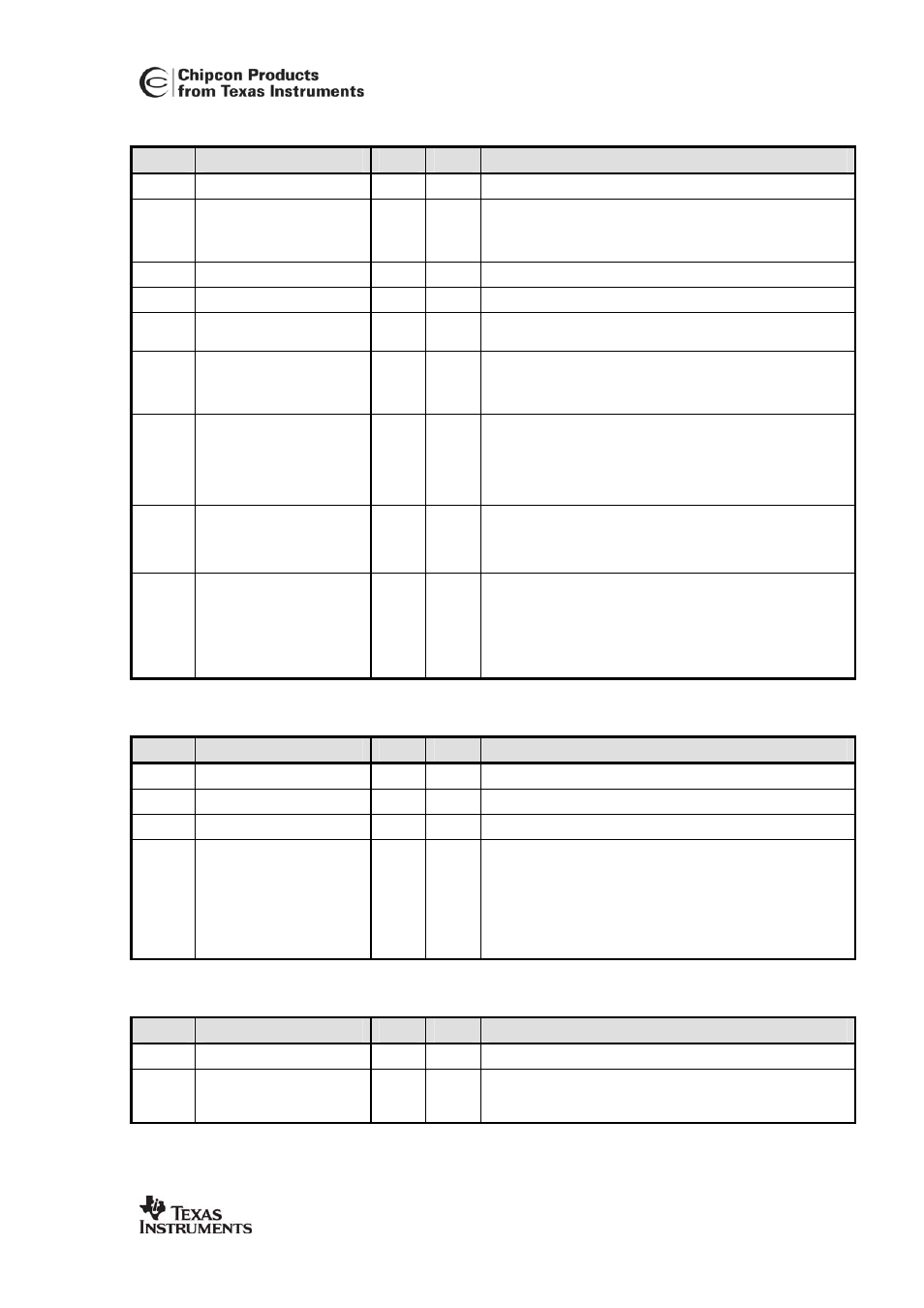

FSTST3 (0x2A) - Frequency Synthesizer Test Register 3

Bit

Field Name

Reset

R/W

Description

15 CHP_CAL_DISABLE 1 R/W

Disable charge pump during VCO calibration when set.

14 CHP_CURRENT_OE

0 R/W

Charge pump current override enable

0 : Charge pump current set by calibration

1 : Charge pump current set by START_CHP_CURRENT

13 CHP_TEST_UP

0 R/W

Forces the CHP to output "up" current when set

12 CHP_TEST_DN

0 R/W

Forces the CHP to output "down" current when set

11 CHP_DISABLE

0 R/W

Set to manually disable charge pump by masking the up and

down pulses from the phase-detector.

10 PD_DELAY

0 R/W

Selects short or long reset delay in phase detector:

0: Short reset delay

1: Long reset delay

9:8

CHP_STEP_PERIOD[1:0] 2 R/W

The charge pump current value step period:

0: 0.25 us

1: 0.5 us

2: 1 us

3: 4 us

7:4

STOP_CHP_CURRENT[3:0] 13 R/W

The charge pump current to stop at after the current is stepped

down from START_CHP_CURRENT after VCO calibration is

complete. The current is stepped down periodically with intervals

as defined in CHP_STEP_PERIOD.

3:0

START_CHP_CURRENT[3:0] 13 R/W

The charge pump current to start with after VCO calibration is

complete. The current is then stepped down periodically to the

value STOP_CHP_CURRENT with intervals as defined in

CHP_STEP_PERIOD.

Also used for overriding the charge pump current when

CHP_CURRENT_OE=’1’

RXBPFTST (0x2B) - Receiver Bandpass Filters Test Register

Bit

Field Name

Reset

R/W

Description

15 -

0 W0

Reserved, write as 0.

14 RXBPF_CAP_OE

0 R/W

RX bandpass filter capacitance calibration override enable.

13:7 RXBPF_CAP_O[6:0]

0

R/W

RX bandpass filter capacitance calibration override value.

6:0 RXBPF_CAP_RES[6:0]

0 R

RX bandpass filter capacitance calibration result.

0: Minimum capacitance in the feedback.

1: Second smallest capacitance setting.

…

127: Maximum capacitance in the feedback.

FSMSTATE (0x2C) - Finite state machine information

Bit

Field Name

Reset

R/W

Description

15:6 -

0

W0

Reserved, write as 0.

5:0 FSM_CUR_STATE[5:0]

0 R

Provides the current state of the FIFO and Frame Control

(FFCTRL) finite state machine. See the Radio control state

machine section on page 43 for details.