Command strobes, Ram access, Cc2420 – Texas Instruments 3138 155 232931 User Manual

Page 29

CC2420

SWRS041B Page 29 of 89

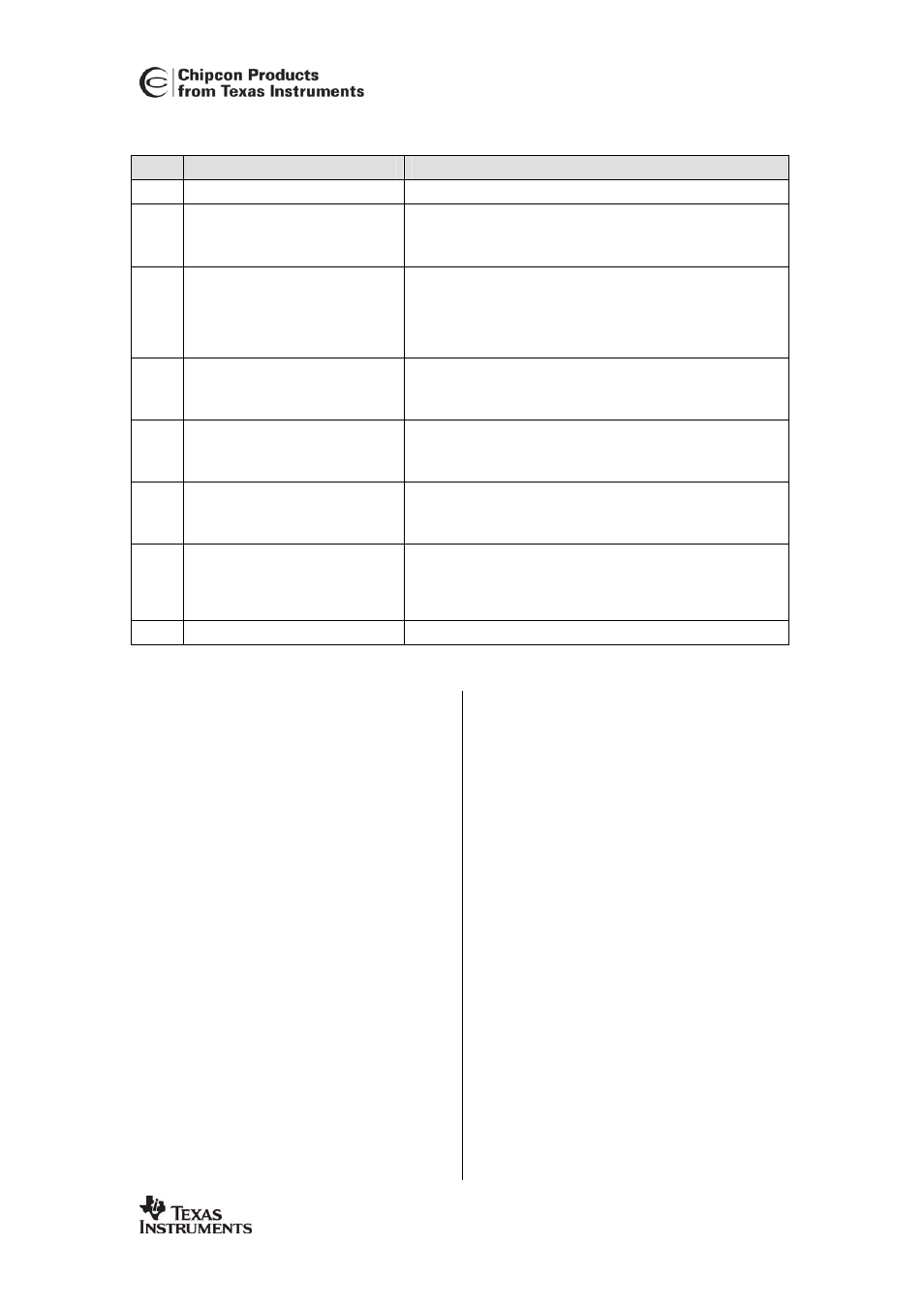

Bit #

Name

Description

7

-

Reserved, ignore value

6

XOSC16M_STABLE

Indicates whether the 16 MHz oscillator is running or not

0 : The 16 MHz crystal oscillator is not running

1 : The 16 MHz crystal oscillator is running

5

TX_UNDERFLOW

Indicates whether an FIFO underflow has occurred during

transmission. Must be cleared manually with a SFLUSHTX

command strobe.

0 : No underflow has occurred

1 : An underflow has occurred

4

ENC_BUSY

Indicates whether the encryption module is busy

0 : Encryption module is idle

1 : Encryption module is busy

3

TX_ACTIVE

Indicates whether RF transmission is active

0 : RF Transmission is idle

1 : RF Transmission is active

2

LOCK

Indicates whether the frequency synthesizer PLL is in lock or not

0 : The PLL is out of lock

1 : The PLL is in lock

1

RSSI_VALID

Indicates whether the RSSI value is valid or not.

0 : The RSSI value is not valid

1 : The RSSI value is valid, always true when reception has been

enabled at least 8 symbol periods (128 us)

0

-

Reserved, ignore value

Table 5. Status byte returned during address transfer and TXFIFO writing

13.4 Command

strobes

Command strobes may be viewed as

single byte instructions to

CC2420. By

addressing a command strobe register

internal sequences will be started. These

commands must be used to enable the

crystal oscillator, enable receive mode,

start decryption etc. All 15 command

strobes are listed in Table 11 on page 62.

When the crystal oscillator is disabled

(Power Down state in Figure 25 on page

44), only the SXOSCON command strobe

may be used. All other command strobes

will be ignored and will have no effect. The

crystal oscillator must stabilise (see the

XOSC16M_STABLE

status bit in Table 5)

before other command strobes are

accepted.

The command strobe register is accessed

in the same way as for a register write

operation, but no data is transferred. That

is, only the RAM/Register bit (set to 0),

R/W bit (set to 0) and the 6 address bits

(in the range 0x00 through 0x0E) are

written. A command strobe may be

followed by any other SPI access without

pulling CSn high, and is executed on the

last falling edge on SCLK.

13.5 RAM

access

The internal 368 byte RAM may be

accessed through the SPI interface. Single

or multiple bytes may be read or written

sending the address part (2 bytes) only

once. The address is then automatically

incremented by the

CC2420 hardware for

each new byte. Data is read and written

one byte at a time, unlike register access

where 2 bytes are always required after

each address byte.

The crystal oscillator must be running

when accessing the RAM.

The RAM/Register bit must be set high to

enable RAM access. The 9 bit RAM

address consists of two parts, B1:0 (MSB)

selecting one of the three memory banks

and A6:0 (LSB) selecting the address

within the selected bank. The RAM is