Unbuffered, serial mode, Cc2420 – Texas Instruments 3138 155 232931 User Manual

Page 40

CC2420

SWRS041B Page 40 of 89

Multiple data frames may be in the

RXFIFO simultaneously, as long as the

total number of bytes does not exceed

128.

See the RXFIFO overflow section on page

33 for details on how a RXFIFO overflow

is detected and signalled.

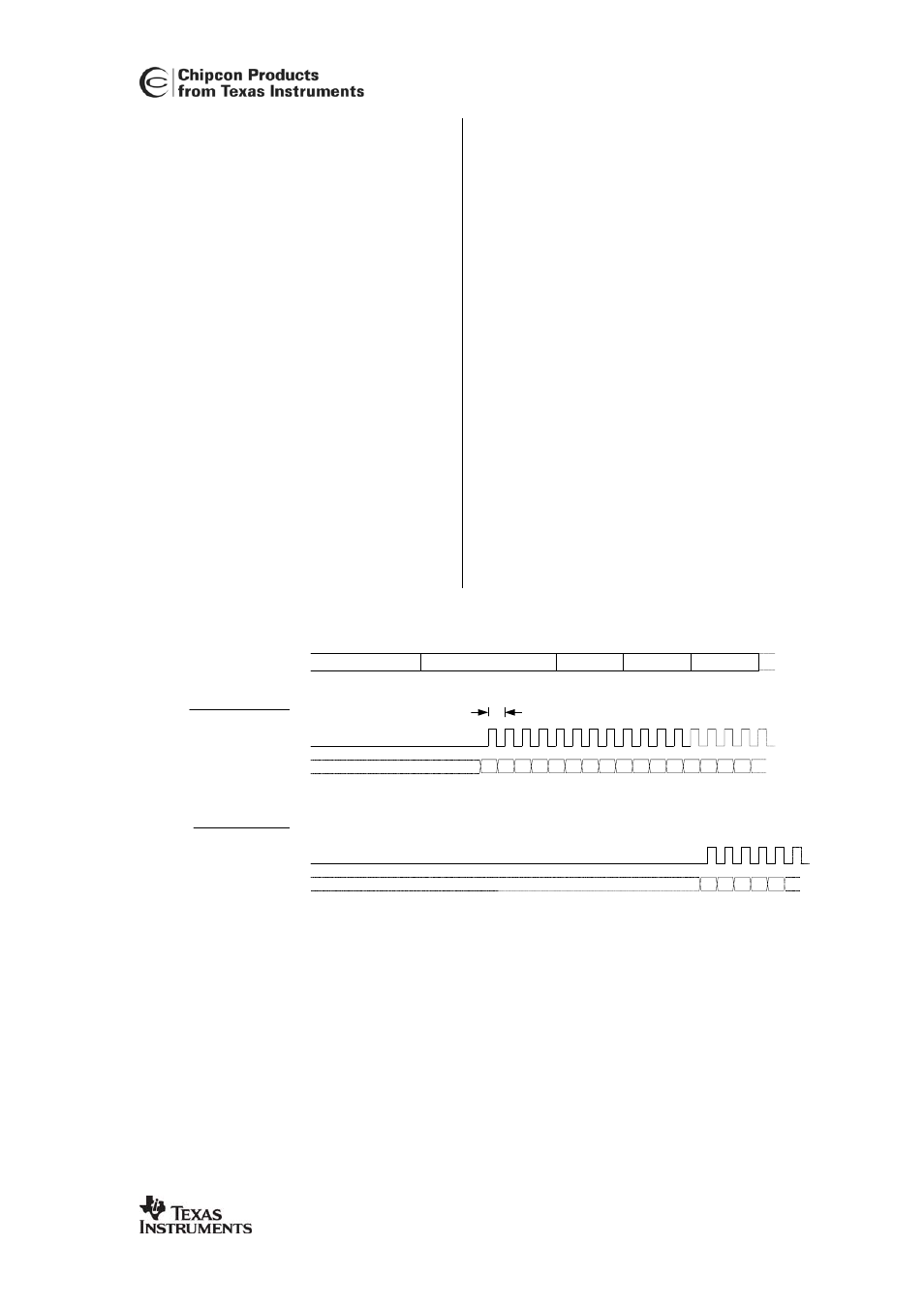

17.3 Unbuffered, serial mode

Unbuffered mode should be used for

evaluation / debugging purposes only.

Buffered mode is recommended for all

applications.

In unbuffered mode, the FIFO and FIFOP

pins are reconfigured as data and data

clock pins. The TXFIFO and RXFIFO

buffers are not used in this mode. A

synchronous data clock is provided by

CC2420

at the FIFOP pin, and the FIFO

pin is used as data input/output. The

FIFOP

clock frequency is 250 kHz when

active. This is illustrated in Figure 22.

In serial transmit mode

(MDMCTRL1.TX_MODE=1), a

synchronisation sequence is inserted at

the start of each frame by hardware, as in

buffered mode. Data is sampled by

CC2420

on the positive edge of FIFOP and should

be updated by the microcontroller on the

negative edge of FIFOP. See Figure 22 for

an illustration of the timing in serial

transmit mode. The SFD and CCA pins

retain their normal operation also in serial

mode.

CC2420

will remain in serial transmit

mode until transmission is turned off

manually.

In serial receive mode

(MDMCTRL1.RX_MODE=1) byte

synchronisation is still performed by

CC2420

. This means that the FIFOP clock

pin will remain inactive until a start of

frame delimiter has been detected.

Receive mode:

Incoming / outgoing

RF data

SFD

FIFOP

Transmit mode:

Preamble

FIFO

(from uC)

b0

b1

b2

b3

b4

b5

b6

b7

b8

b9 b10 b11

s0

s1

FIFOP

FIFO

(from

CC2420

)

b0

b1

b2

b3

b4

s2

b8

b9 b10 b11

4 us

Figure 22. Unbuffered test mode, pin activity