Texas Instruments TLV1562 User Manual

Page 8

The Board

2

SLAA040

2.2

TLV1562EVM

The TLV1562EVM gives customers an easy start with employing many of the

features of this converter. A serial DAC (TLC5618A), a parallel DAC (THS5651),

and the ADC (TLV1562) make this EVM flexible enough to test the features of the

TLV1562. It also helps show how this ADC can be implemented.

2.3

ADC TLV1562 Overview

The TLV1562 is a CMOS 10-bit high-speed programmable resolution analog-to-

digital converter, using a low-power recyclic architecture.

The converter provides two differential or four single-ended inputs to interface the

analog input signals.

On the digital side, the device has a chip-select (CS), input clock (CLKIN),

sample/conversion start signal (CSTART), read signal input (RD), write signal

input (WR), and 10 parallel data I/O lines (D9:0).

The converter integrates the CSTART signal to coordinate sampling and

conversion timing without using the parallel bus. Since the TMS320C542 DSP

has no second general-purpose output, this signal is generated with the signal

(CSTART) from the address decoder.

2.3.1

Suggestions for the ’C54x to TLV1562 Interface

The following paragraphs describe two suggested interfaces between the ’C54x

and the TLV1562.

2.3.1.1

The Universal Interface

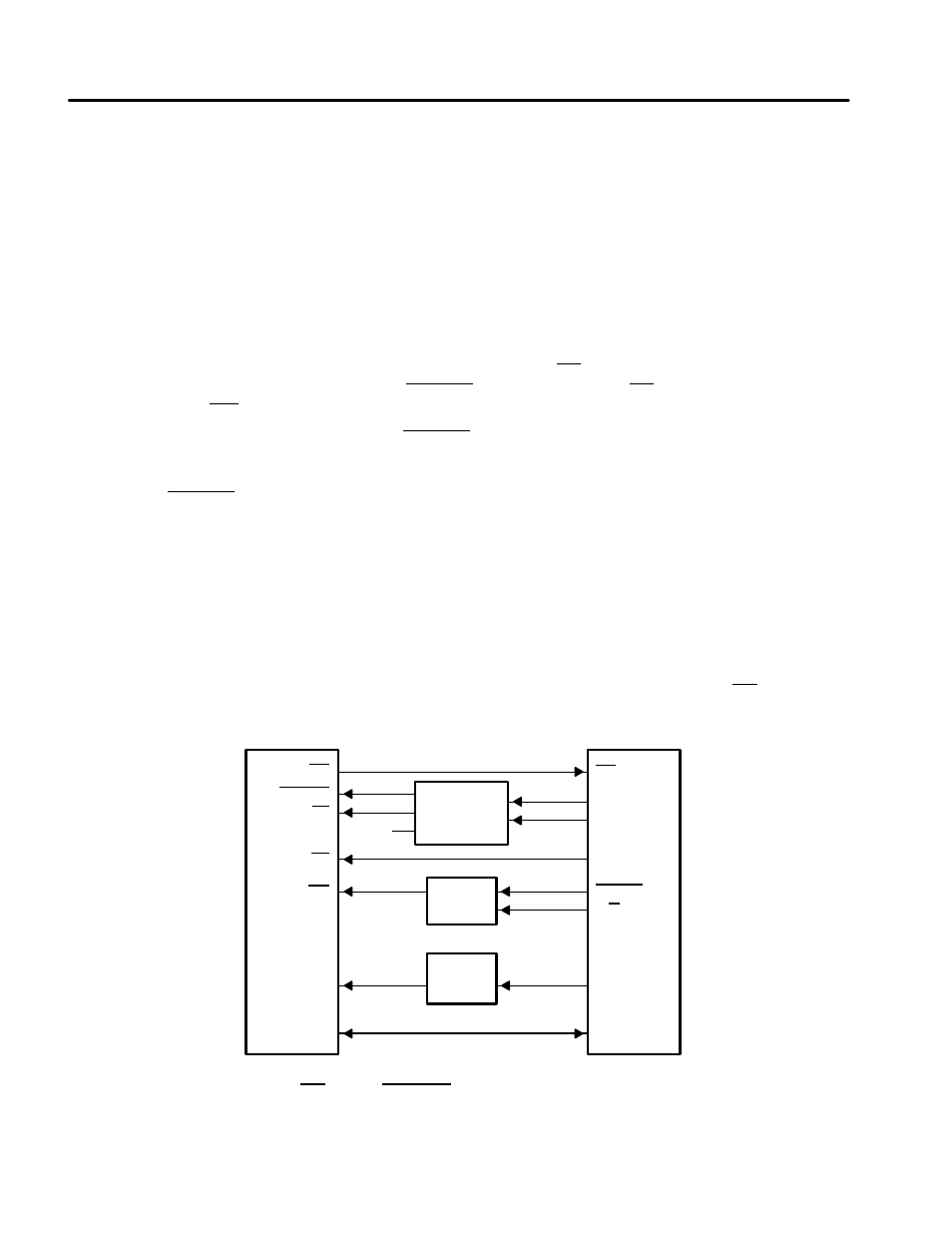

The schematic in Figure 1 shows the pin-to-pin connections between the

TLV1562 and ’C54x, realized on the EVM. This routing can test the converter in

each mode. One I/O-wait state is required for write operations to the ADC. The

read sequence from the ADC does not require any wait states because the RD

signal is generated with XF.

Address

Decoder

01

10

11

≥

1

1: x

Divider

INT

CSTART

CS

RD

WR

CLKIN

D(0–9)

D(0–9)

CLOCKOUT

R/W

IOSTRB

XF

A1

A0

INT

TLV1562

TMS320C54x

Figure 1. TLV1562 to ’C54x DSP Interface of the EVM,

Using RD or the CSTART Signal to Start Conversion