Texas Instruments TLV1562 User Manual

Page 19

Conversation Between the TLV1562 and the DSP

13

Interfacing the TLV1562 Parallel ADC to the TMS320C54x DSP

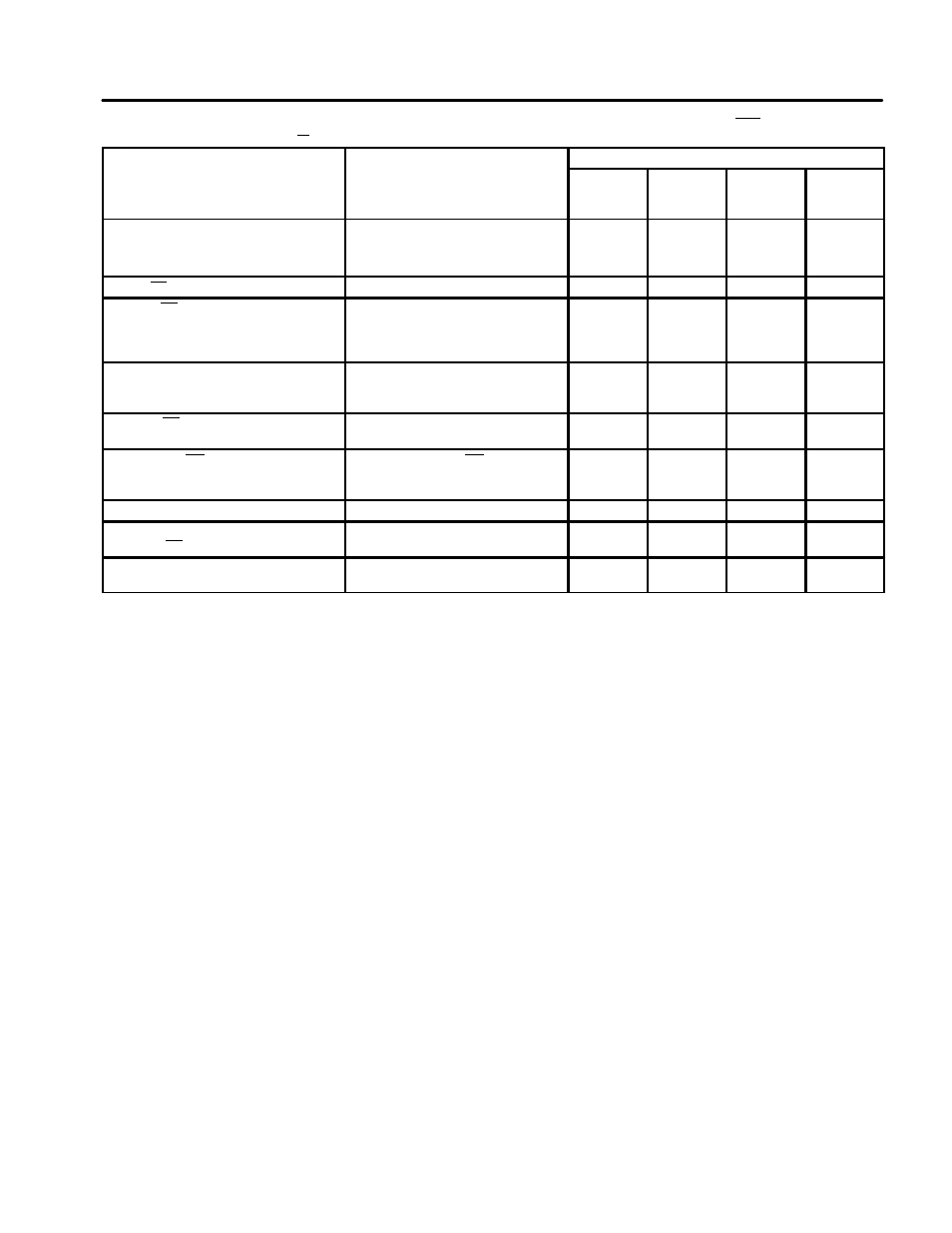

Table 7. DSP Algorithm for Mono Interrupt Driven Mode Using RD

Wait cycles for the DSP internally (40 MHz DSPCLK):

STEPS

TIMING, NOTES

APD=0

ADCSYCLK

= 7.5 MHz

APD=0

ADCSYCLK

= 10 MHz

APD=1

ADCSYCLK

= 10 MHz

APD=1

ADCSYCLK

= 10 MHz

0.

Initialization

Write all configuration data to the

ADC

activate the mono interrupt-driven mode

in CR0(2;3)

1.

set CS

deselect ADC (optional with APD=0)

2.

clear CS

Select ADC

(Note: if Hardware Auto power down is

enabled, Chip select has to be used,

otherwise CS can be left high)

3.

Wait for

t

D(CSL-sample)

+1ADCSYSCLK

t

D(CSL-sample)

= 5ns (APD=0)

t

D(CSL-sample)

= 500ns (APD=1)

≥

6

≥

5

≥

26

≥

25

4.

Clear RD

ADC goes over from sampling into

conversion

5.

Wait until INT goes low

alternative: ignore the INT signal, wait 49

ns+5(6) ADCSYSCLK and goto step

number 7

≥

34

≥

22

≥

34

≥

22

6.

Wait the time t

EN(DATAOUT)

t

EN(DATAOUT)

= 41 ns

≥

2

≥

2

≥

2

≥

2

7.

Read sample out from the data port;

Reset RD signal

8.

Goto step 1 or step 3 (if APD=0) for

more samples