3 connections between the dsp and the evm – Texas Instruments TLV1562 User Manual

Page 13

Operational Overview

7

Interfacing the TLV1562 Parallel ADC to the TMS320C54x DSP

3.3

Connections Between the DSP and the EVM

The following connections provide the interface between the DSP and the EVM:

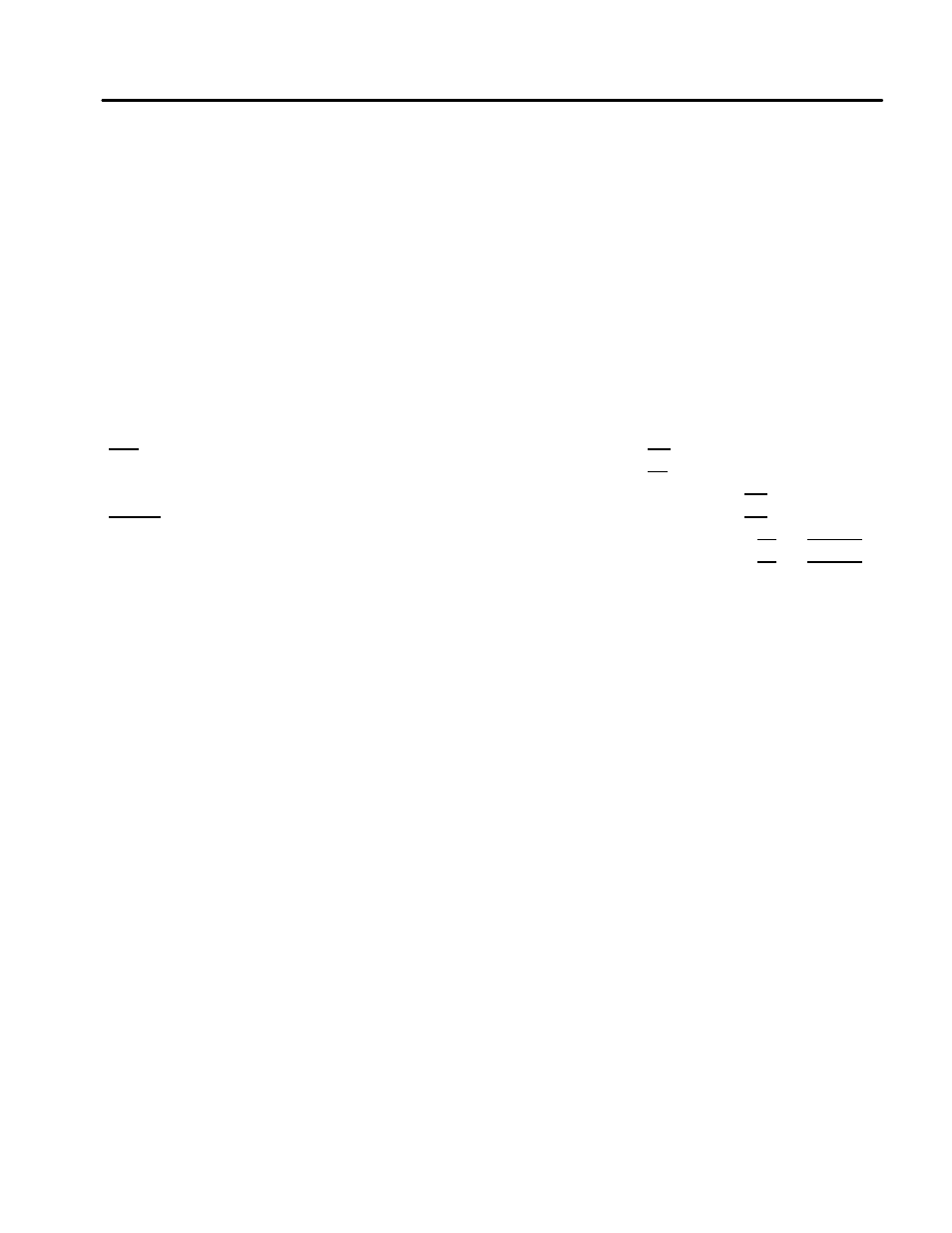

Table 1. Signal Connections

DSP Signal

Connector/Pin on the DSKplus cir-

cuit board

Connector/Pin on

the TLV1562EVM

ADC Signal

General

GND

Connector JP4: Pin 1, 10, 11, 12, 14,

15, 19, 20, 21, 27, 34, 35

Connector JP5: Pin 6, 10, 11, 12

J10/2,J10/4,...,J10/34

J11/4,J11/6,...,J11/26

GND

VCC

JP1/32

N/A

VCC

Parallel Interface

CLKOUT

JP3/2

J11/11

CLKIN

INT0

JP5/1

J11/5

INT

XF

JP4/8

J11/3

RD

R/W

JP4/30

J11/9

decoded to the WR line

IOSTRB

JP4/36

J11/7

decoded to the WR line

A0

JP5/34

J11/2

addr. decoder for CS and CSTART

A1

JP5/35

J11/1

addr. decoder for CS and CSTART

D0

JP3/35

J10/13

D0

D1

JP3/34

J10/15

D1

D2

JP3/8

J10/17

D2

D3

JP3/12

J10/19

D3

D4

JP3/11

J10/21

D4

D5

JP3/15

J10/23

D5

D6

JP3/14

J10/25

D6

D7

JP3/18

J10/27

D7

D8

JP3/17

J10/29

D8

D9

JP3/21

J10/31

D9

Serial Interface to the DAC TLC5618A

BCLKR

JP1/14

J11/25

SCLK

BCLKX

JP1/17

J11/23

SCLK

BFSR

JP1/20

J11/21

CS

BFSX

JP1/23

J11/19

CS

BDR

JP1/26

J11/17

DIN

BDX

JP1/29

J11/15

DIN

Signals D[9–0] of the TLV1562 and D[9–0] of the DSP are tied together in this

application to simplify hardware debugging during the development phase.

However, if the 2s complement feature of the DAC is to be used, it is easier to

connect D[15-6] of the DSP with D[9–0] of the ADC. A simple right shift of the

result then evaluates the result when sign extension mode (SXM) is enabled.