4 onboard components – Texas Instruments TLV1562 User Manual

Page 10

The Board

4

SLAA040

This feature fits well into monitoring application. For example, the ADC may have

to trigger on one event out of some channels inside an extremely small time

window and then sample the correct channel with a higher resolution, but lower

throughput to analyze this process. This feature also fits well into home security

applications or applications that must monitor several inputs simultaneously.

2.3.3

Note on the Interface, Using an External ADC Clock Drive

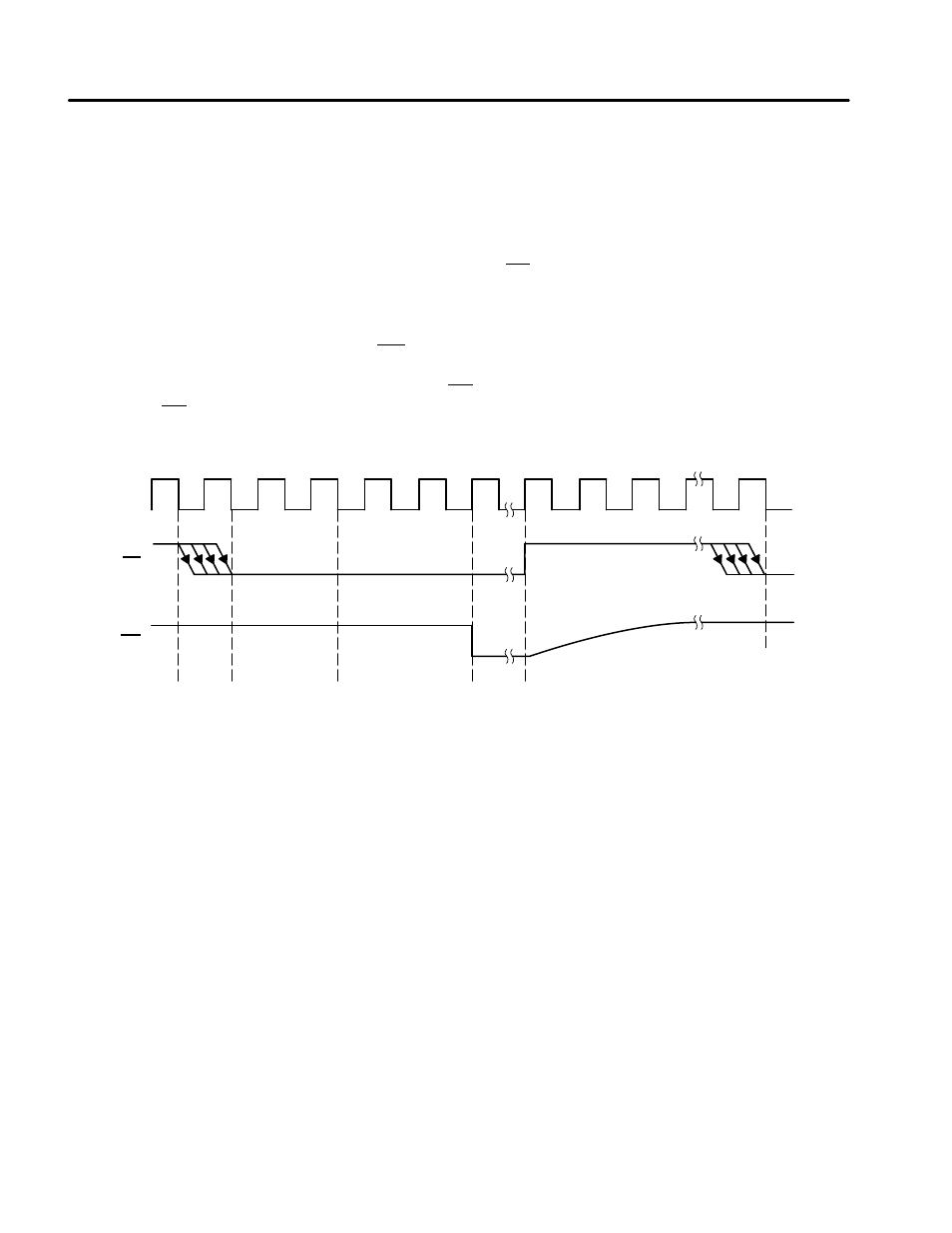

The TLV1562data sheet (Figure 9) shows that RD has to fall as close as possible

to the falling edge of the clock signal. The user must adhere to this timing,

otherwise the conversion result may be wrong. The user may not recognize the

erroneous result, since the ADC will signal that the conversion has finished during

the logic low transition of the INT signal. The following timing diagram shows the

interface behavior of the ADC whether the timing is correct or not. The following

figure shows what happens when the RD falling edge is timed wrong. Although

RD falls nearly 1/2 of one cycle too late, the conversion result is valid on the 5

th

clock cycle.

1

2

3

4

5

6

7

8

9

10

CLK

1

RD

INT

Conversion Starts

Next Sampling Starts

Conversion Finished

2.4

Onboard Components

These sections describe the EVM onboard components.

2.4.1

TLC5618A – Serial DAC

This 12-bit DAC has a serial interface that can run at 20-MHz clock; therefore, it

can update the output at 1.21 MSPS. Two outputs are available on the 8-pin

package. The buffered SPI of the DSP provides the DSP interface. Using the

auto-buffer mode, updating the data on the DAC requires only four CPU

instructions/samples.