Renesas CPU Board M3A-HS19 User Manual

Page 25

Features and Specifications

2.3.3 External Synchronous DRAM

Rev.1.01 Oct 28, .2008

2-9

REJ10J1351-0101

2

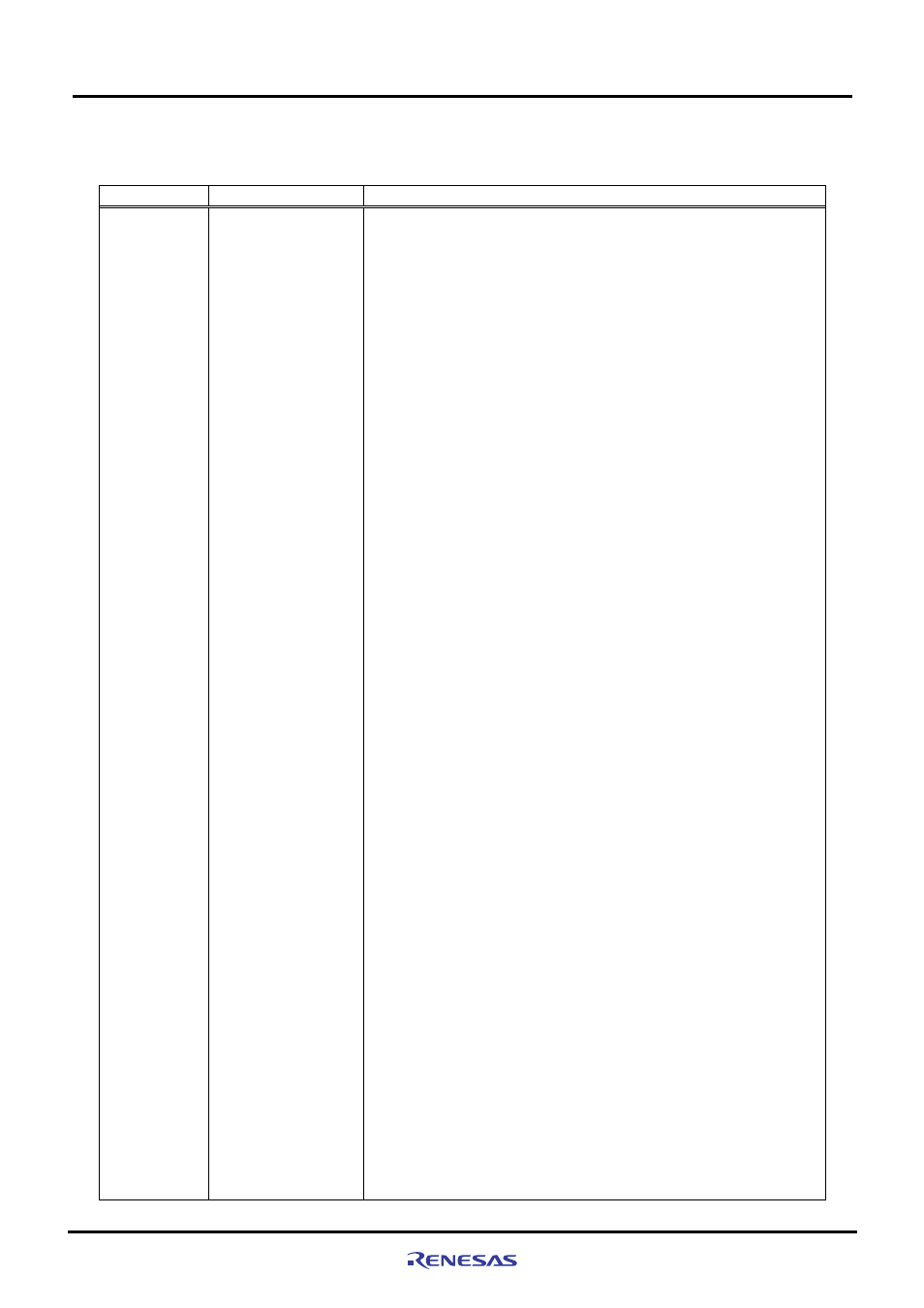

Table2.3.5 lists setting examples of the bus state controller with SH7619 bus clock at 62.5 MHz.

Figure 2.3.5 shows the SDRAM single read/write timing example.

Table2.3.5 Setting Example of Bus State Controller (SDRAM Read/Write)

User Area

Applicable Device

Settings for Bus State Controller

CS3 EDS1216AATA-75E

CS3

Space

Bus Control Register: CS3BCR

Initial value: H'36DB 0600

Recommended value: H'0000 4400 (in 16-bit bus width)

• Memory specification

TYPE[3:0] = B'0100; SDRAM

• Data bus specification

BSZ[1:0] = B'10; 16-bit bus width

CS3 Space Wait Control Register: CS3WCR

Initial value: H'0000 0500, recommended value: H'0000 2892

• Wait Cycle Number for Precharge Completion

WTRP[1:0] = B'01; 1 cycle

• Wait Cycle Number from ACTV command to READA WRITA

command

WTRCD[1:0] = B'10; 2 cycles

• Cas Latency for Area 3

A3CL[1:0] = B'01; 2 cycles

• Wait Cycle Number for Precharge Start Wait

TRWL[1:0] = B'10; 2 cycles

• Idle Cycle Number from REF/Self-Refreshing Release to

ACTV/REF/MRS Command

WTRC[1:0] = B'10; 5 cycles

SDRAM Control Register: SDCR

Initial value: H'0000 0000,

Recommended value: H'0000 0809

• Refresh Control

RFSH = B'1; Refreshing is performed

• Refresh Control

RMODE = B'0; Auto-Refreshing is not performed

• Bank active mode

BACTV = B'0; Auto-precharge mode

• Number of Bits of Row Address for Area 3

A3ROW[1:0] = B'01; 12 bits

• Number of Bits of Column Address for Area 3

A3COL[1:0] = B'01; 9 bits

Refresh Timer Control / Status Register: RTCSR

Initial value: H'0000 0000,

Recommended value: H'A55A 0010

• Clock Select

CKS[2:0] = B'010; B

φ/16

• Refresh Count

RRC[2:0] = B'000 ; Once

Refresh Time Constant Register: RTCOR

Initial value: H'0000 0000,

Recommended value: H'A55A 003D

*The refresh request interval when clock select is set to B

φ/16 is as

follows.

1 cycle: 256 nsec (62.5 MHz/16 = 3.90625 MHz)

Refresh request interval in this SDRAM: 15.625

μsec/time

15.625 usec/256 nsec = 61 (0x3D) cycles/refresh counts