11 watchdog timer initialization cycle check pin, 1 check pin wrst (tp3) on the emulator main unit, Important – Renesas Compact Emulator M34571T2-CPE User Manual

Page 41

M34571T2-CPE User’s Manual

2. Setup

REJ10J0972-0100 Rev.1.00 February 10, 2006

Page 39 of 72

2.11 Watchdog Timer Initialization Cycle Check Pin

The watchdog time cannot be used with this emulator system. The watchdog timer initialization cycle can be verified by

observing the waveform at the check pin (WRST) of the emulator.

2.11.1 Check Pin WRST (TP3) on the Emulator Main Unit

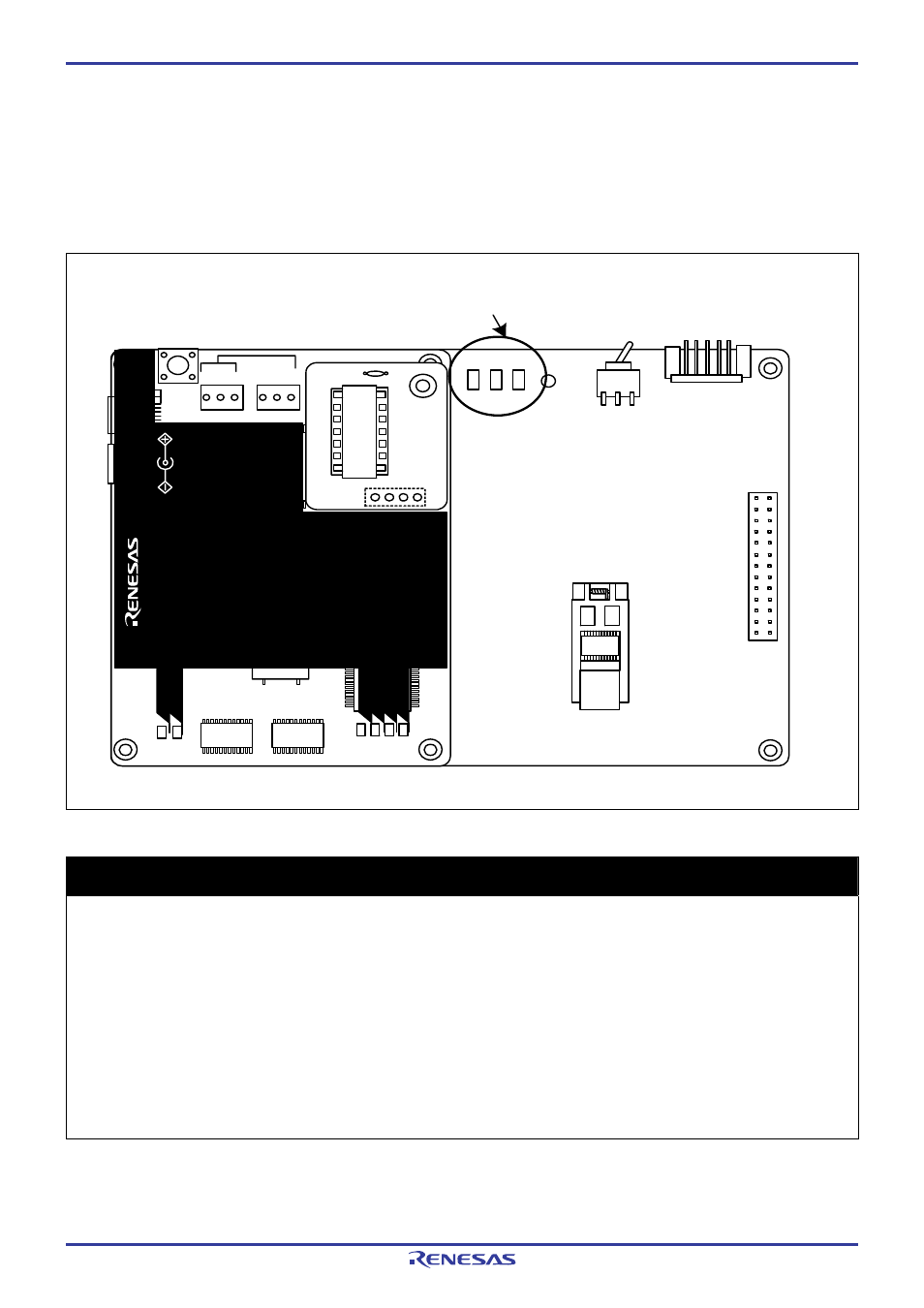

Figure 2.19 shows the positions of the check pins WRST (TP3) and GND (TP2).

Figure 2.19 Positions of the check pins

IMPORTANT

Notes on the Watchdog Timer Function:

In this emulator system, the watchdog timer function must be invalid during debugging operation; it is,

therefore, necessary to invalidate the watchdog timer by prefixing the following two instructions to the user

program continuously:

DWDT

WRST

In case where no watchdog timer invalid processing as described above is carried out, there arise restrictions as

described below:

- In case where the MCU was reset during user program run execution, program stop and break cannot be

performed normally after that.

During debugging operation, be sure to execute the afore-mentioned watchdog timer invalid processing.

M34571T2 -CPEB REV. A

TP

1

VDD

2

GN

D

TP

2

W

RS

T

PO

F

LE

D

1

PO

W

E

R

SA

FE

ST

AT

U

S

J4

3V

5V

SW

1

J3

13

14

1

26

MA

DE

PO

W

E

R

CO

MP

A

CT

EMU

LAT

OR

CL

O

C

K

RE

S

E

T

RU

N

LE

D

3

LE

D

6

L

E

D

5LE D

4

PO

W

E

R

SA

F

E

LE

D

2

LE

D

1

SA

FE

POW

E

R

PO

W

ER

CLO

C

K

RE

SE

T

RUN

M

345

71T

2-

C

PE

STA

T

U

S

SY

ST

E

M

ST

AT

U

S

TAR

G

ET

MADE

IN

J

A

P

A

N

CO

M

P

ACT

E

M

U

L

A

T

O

R

PO

W

E

R

5.

0

V

US

B

IN

T

3.

3V

5.

0V

JP

1

JP

2

EXT

Check pins TP1: VDD2

TP2: GND

TP3: WRST