NEC PD78058FY(A) User Manual

Page 486

486

CHAPTER 21 INTERRUPT AND TEST FUNCTIONS

Address

FFECH

00H

After

Reset

R/W

R/W

0

0

1

1

INTP0 Valid Edge Selection

Falling edge

Rising edge

Setting prohibited

Both falling and rising edges

ES11

7

ES31

Symbol

INTM0

6

ES30

5

ES21

4

ES20

3

ES11

2

ES10

1

0

0

0

0

1

0

1

ES10

0

0

1

1

INTP1 Valid Edge Selection

Falling edge

Rising edge

Setting prohibited

Both falling and rising edges

ES21

0

1

0

1

ES20

0

0

1

1

INTP2 Valid Edge Selection

Falling edge

Rising edge

Setting prohibited

Both falling and rising edges

ES31

0

1

0

1

ES30

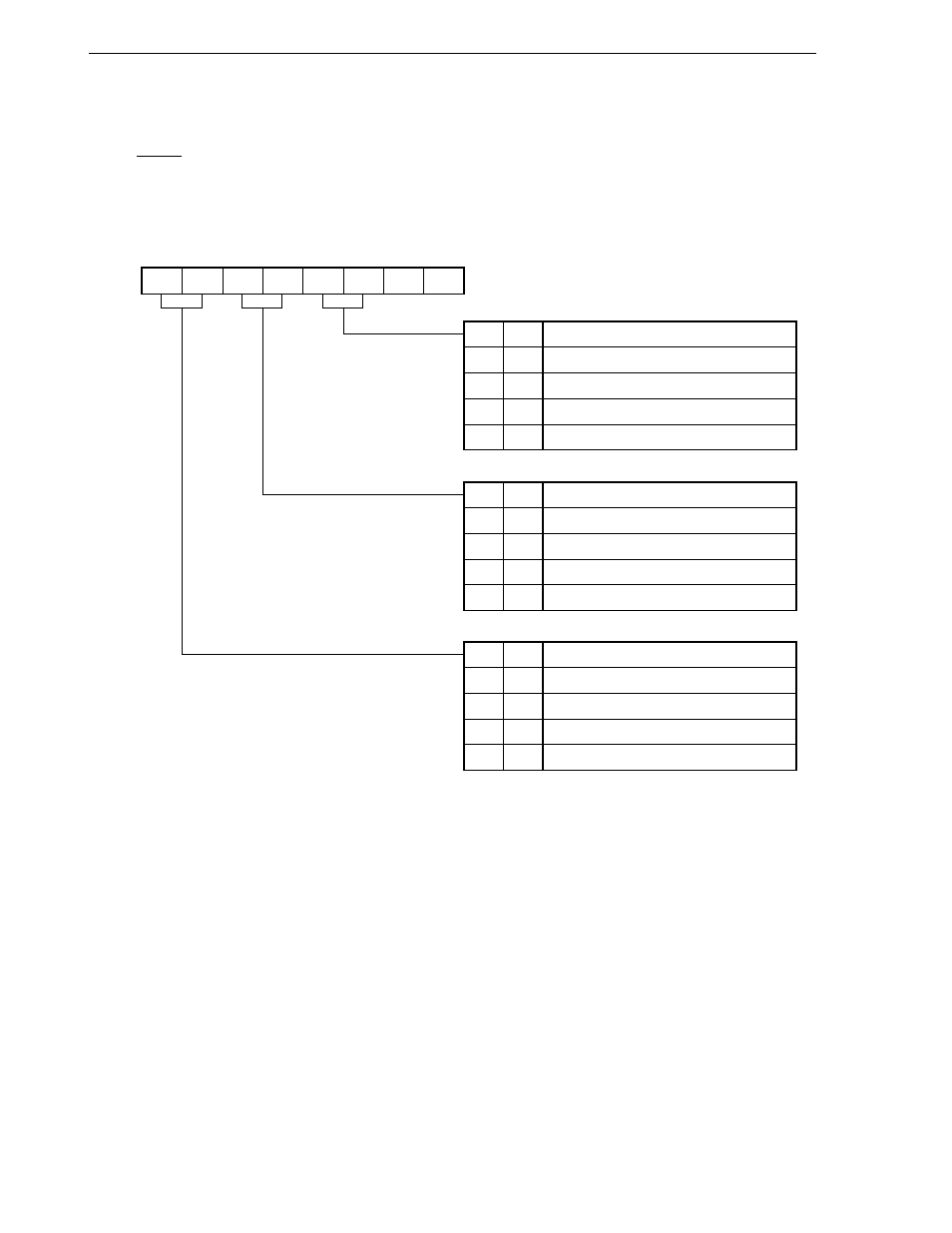

(4) External interrupt mode register (INTM0, INTM1)

These registers set the valid edge for INTP0 to INTP6.

INTM0 and INTM1 are set by 8-bit memory manipulation instructions.

RESET input sets these registers to 00H.

Figure 21-5. External Interrupt Mode Register 0 Format

Caution

Set the valid edge of the INTP0/TI00/P00 pin after setting bits 1 to 3 (TMC01 to TMC03)

of the 16-bit timer mode control register (TMC0) to 0, 0, and 0, respectively, and then

stopping timer operation.