Figure 5-8. ctr1gate signal timing requirements, Counter 1 internal output signal, Figure 5-9. ctr1internaloutput signal behavior – National Instruments Data Acquisition Device E Series User Manual

Page 113: Counter 1 internal output signal -8

Chapter 5

Counters

5-8

ni.com

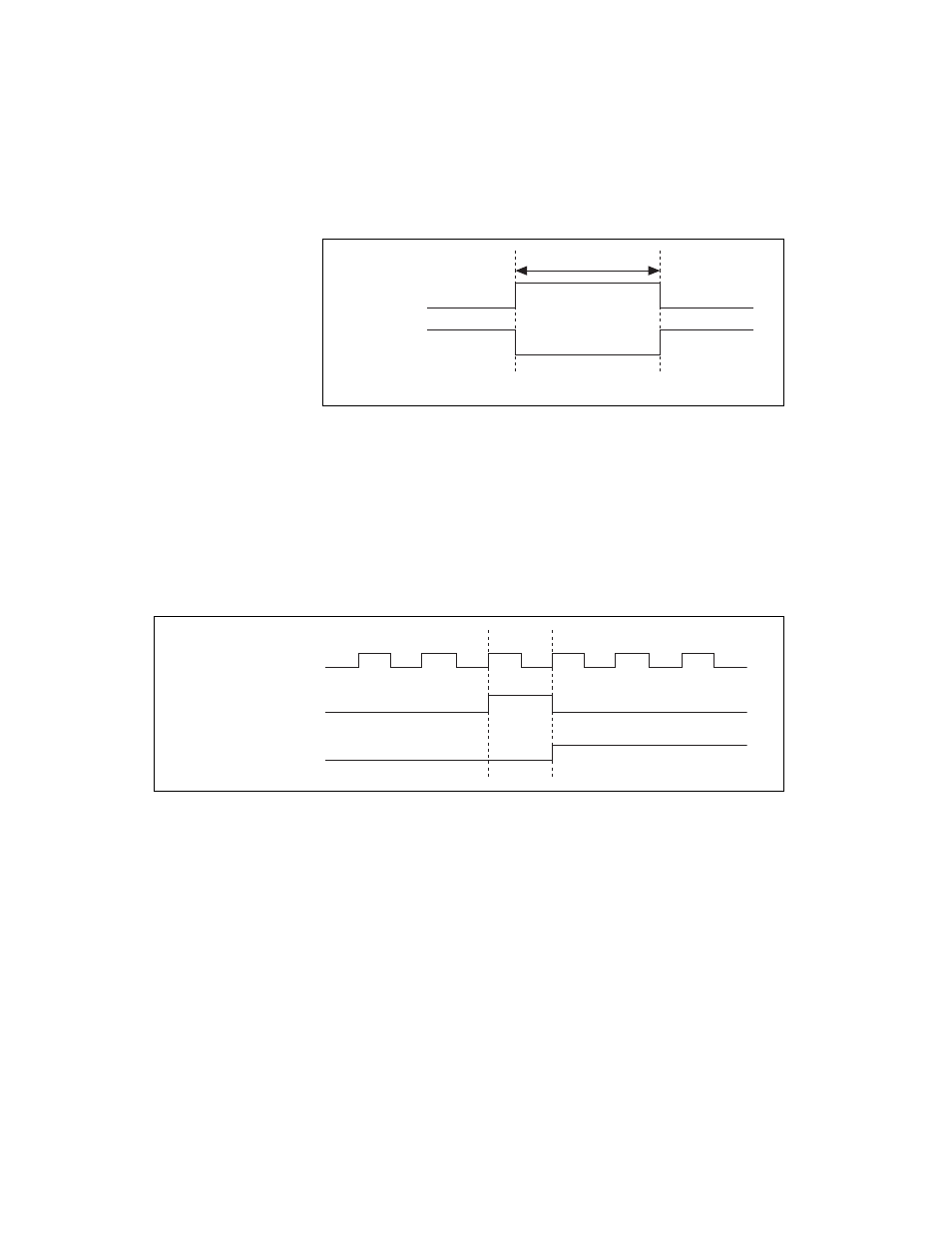

Figure 5-8 shows the timing requirements for the Ctr1Gate signal.

Figure 5-8. Ctr1Gate Signal Timing Requirements

Counter 1 Internal Output Signal

The Counter 1 Internal Output (Ctr1InternalOutput) signal is the output of

Counter 1. This signal reflects the terminal count (TC) of Counter 1. The

counter generates a terminal count when its count value rolls over. The

two software-selectable output options are pulse on TC and toggle output

polarity on TC. The output polarity is software-selectable for both options.

Figure 5-9 shows the behavior of the Ctr1InternalOutput signal.

Figure 5-9. Ctr1InternalOutput Signal Behavior

You can use Ctr1InternalOutput in the following applications:

•

In pulse generation mode, the counter drives Ctr1InternalOutput with

the generated pulses. To enable this behavior, software configures the

counter to toggle Ctr1InternalOutput on TC.

•

Ctr1InternalOutput can control the timing of analog output

acquisitions by driving ao/SampleClock.

•

Counter 0 and 1 can be daisy-chained together by routing

Ctr1InternalOutput to Ctr0Gate.

Rising-Edge

Polarity

Falling-Edge

Polarity

t

w

t

w

= 10 ns minimum

Ctr0Source

Ctr0InternalOutput

(Pulse on TC)

Ctr0InternalOutput

(Toggle Output on TC)

TC